Hi All,

I have question about platform for OpenMP to TMS320C6678

Into TI documentations about OpenMP by talks "Be aware that breaking these rules might result in an application that builds

fine but might (arbitrarily) malfunction at runtime" - ti/omp_1_01_03_02/docs/User Guide.pdf and

"If ‘dataMemory’ is set to a memory segment that lies in the physical address

range for MSMC RAM (0x0C000000), then L1D must be set to ‘0K’ to make this

address range non-cacheable".

Into file ti/omp_1_01_03_02/packages/ti/omp/examles/platforms/evm6678/Platform.xdc there is next:

/*!

* File generated by platform wizard. DO NOT MODIFY

*

*/

. . . .

["MSMCSRAM_NOCACHE", {name: "MSMCSRAM_NOCACHE", base: 0xA0100000, len: 0x00300000}],

],

l1DMode:"32k",

l1PMode:"32k",

l2Mode:"0k",

});

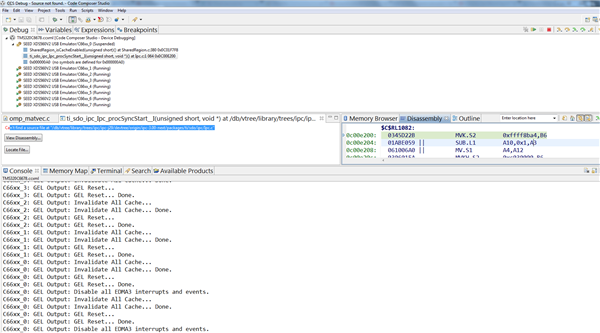

I trued run OMP exapmle with ti.omp.examples.platforms.evm6678 and receive

with ti.omp.examples.platforms.evm6678_ddr all examples run successfully

My question - this is contradiction into documentation or I understand something wrong?

Best Regards,

Oleg