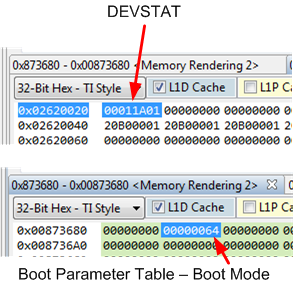

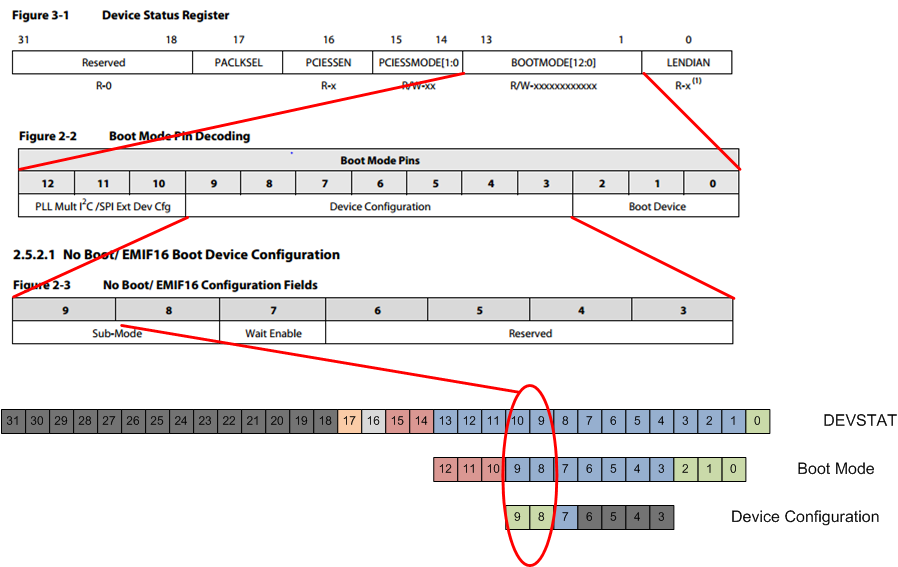

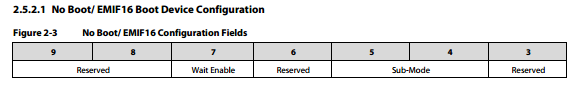

I can't seem to get my C6671 to boot directly out of NOR flash that is connected directly to the EMIF bus. Below is a screen shot of the DEVSTAT register. I believe it shows the boot device as "EMIF16/No Boot" with the sub-mode of "EMIF16 boot". The hardware never seems to try to read 0x70000000. When I read the boot parameter table it always has 0x64 which is 100 or "Sleep Boot Mode". I was expecting it to be 70 which is "EMIF16 Boot Mode". What am I missing?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.