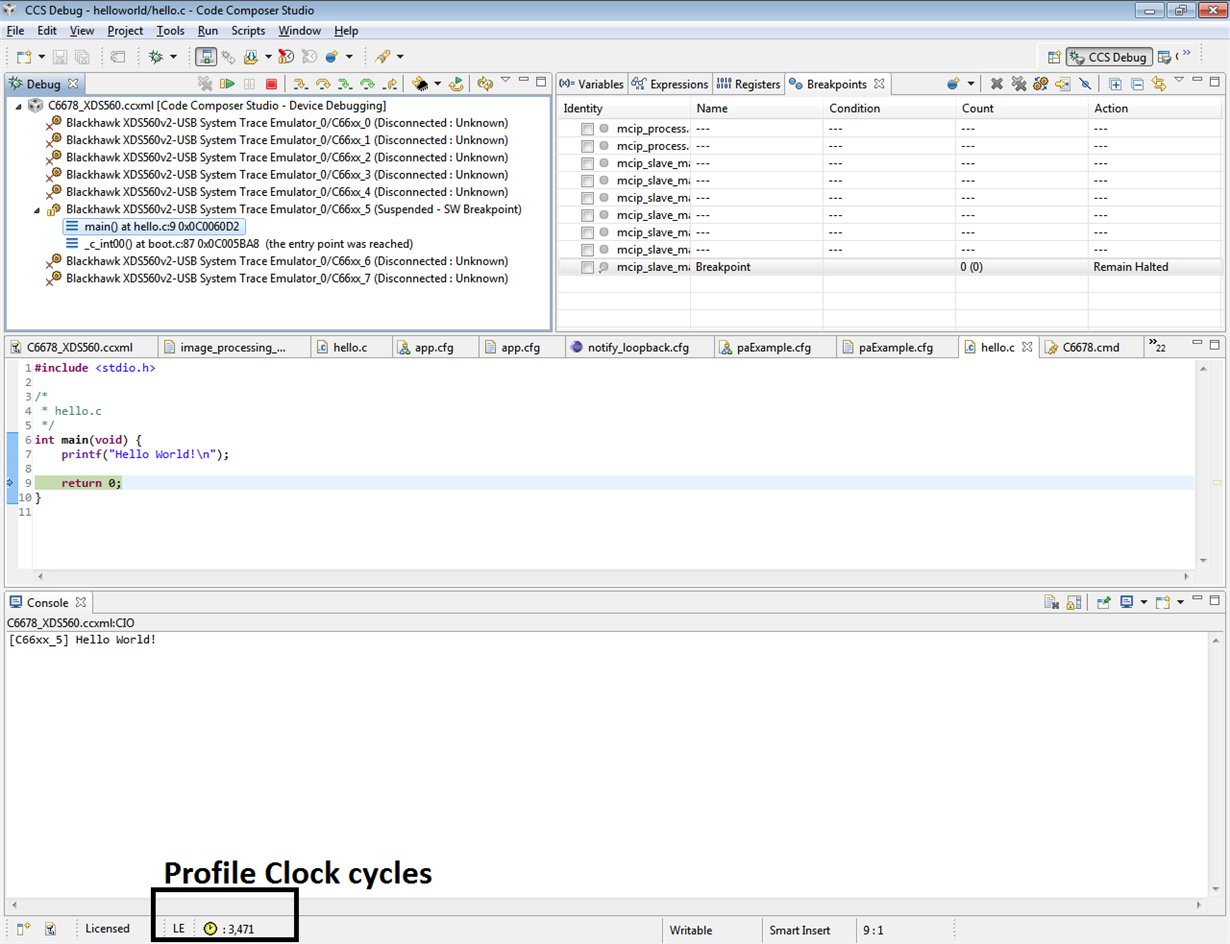

I have a question in C6678 , help me please ...

8 cores (core 0 ~ core 7) perform the same algorithm, and also the same input data.

The problem is that the execution time differs among core 0 ~ core 7.

Core 0 = Core 1 = Core 2 = Core 3 = Core 4 ==> about 3.8 second

Core 5 = Core 6 = Core 7 ==> about 10.8 second

Why core[0:4] and core[5:7] execution time is inconsistency?

(I using CCS 5.4, MCSDK 2.1.2.6, SYS/BIOS 6.35.1.29, and compiler 7.4.6.)