Hi,

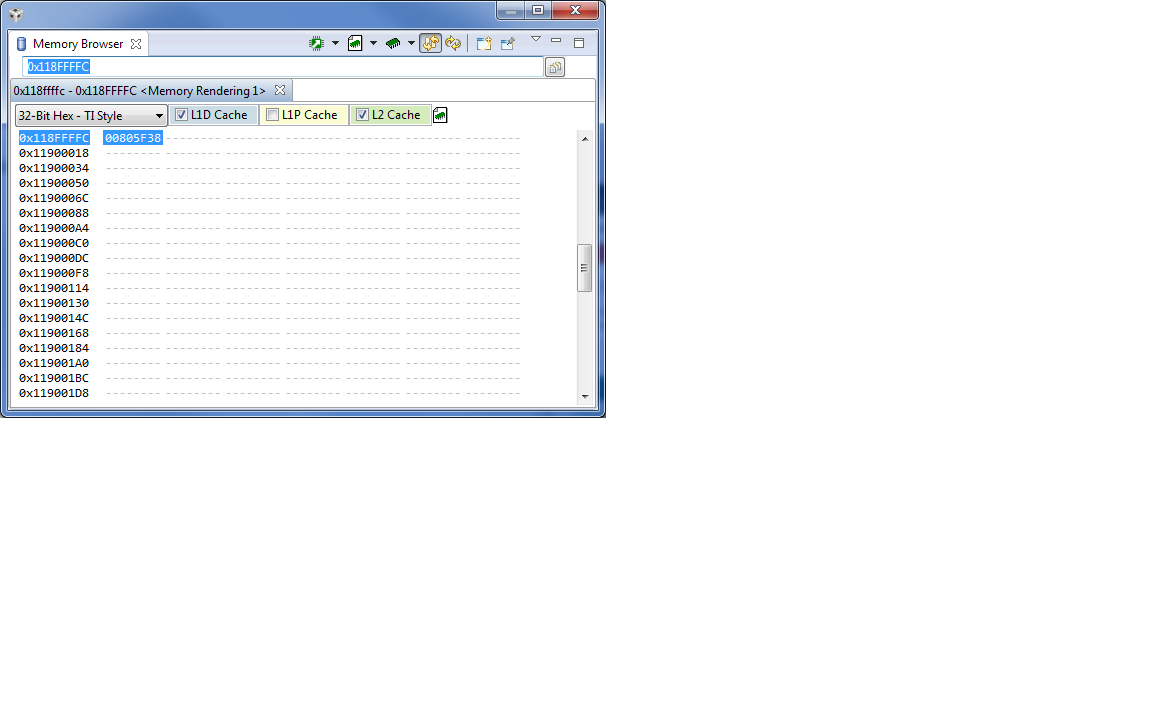

i am using EVM6657 with CCSV5.5 and trying to test srioboot_helloworld_evmc6657l example . i try to run second core, so one of the TI people told me to use this example. i am using this example but core 0 will not start core 1. i debugged and found that i can't able to write in KICK0,KICK1 and IPCGR registers. they are zeroes. i hope the TI has already tested this program.please tell me why this is not working?

do i have to change any code composer version, as i am using now CCSV5.5 with bios 6.35.4.50.

Thanks,

Ram.