Hello, all,

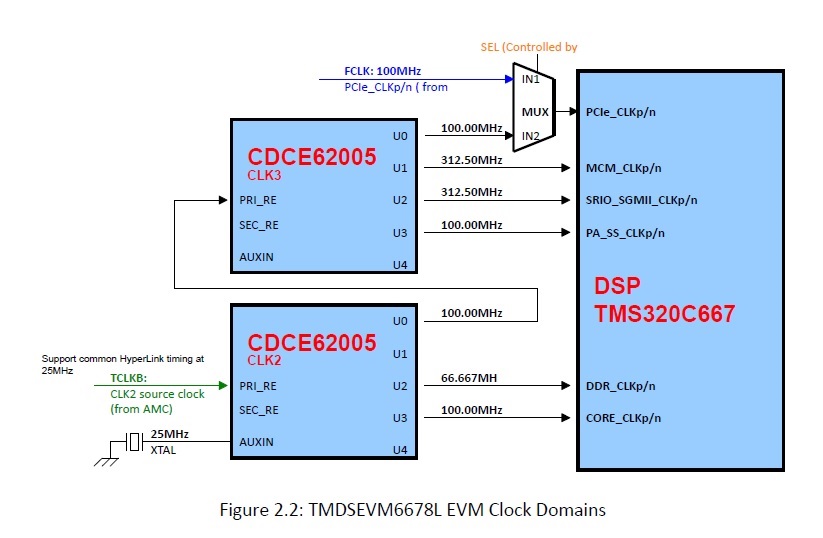

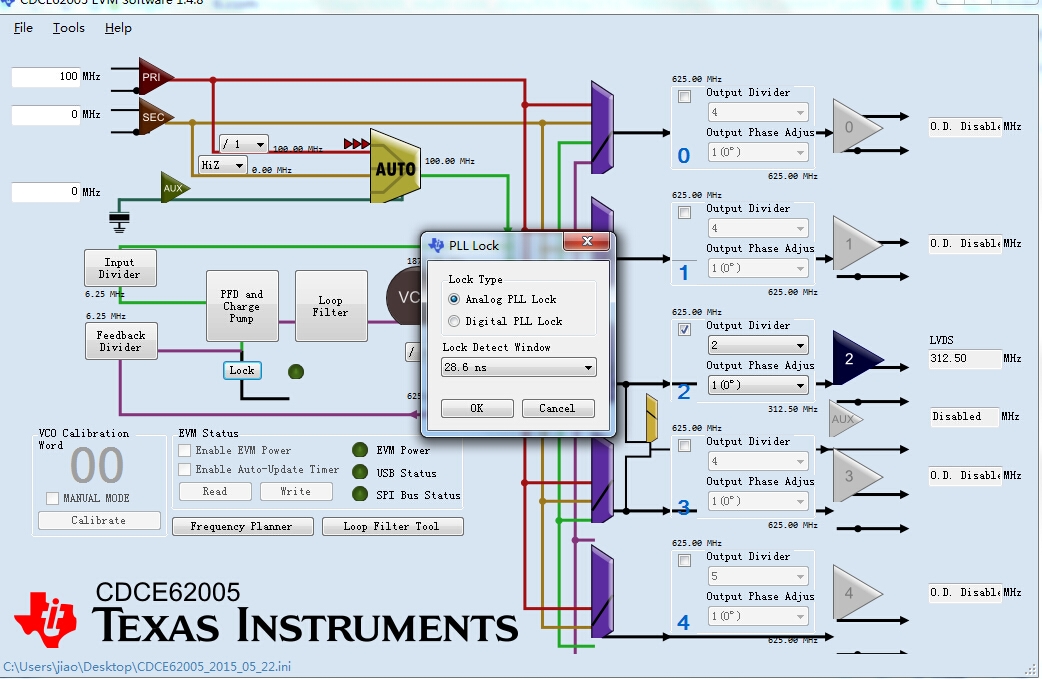

I designed a board based on EVM6678, now I face a problem, the SGMII can't work well. I have asked for many suggestions, someone said it's because the instability of clock. I used the software to config the register, but the pll is still unlocked, and I don't know how to make the clock in a better condition. Someone can give me some advice? Thank you very much!!!