Hello,

My customer is developing their system with C6655 and using its uPP in receive mode (16bit).

They are getting stuck with very strange behavior...

We need to clarify uPP behavior. uPP is very very important transport in their application.

Hope you could reply soon.

So, here is the problem.

C6655 does not receive incoming data correctly.

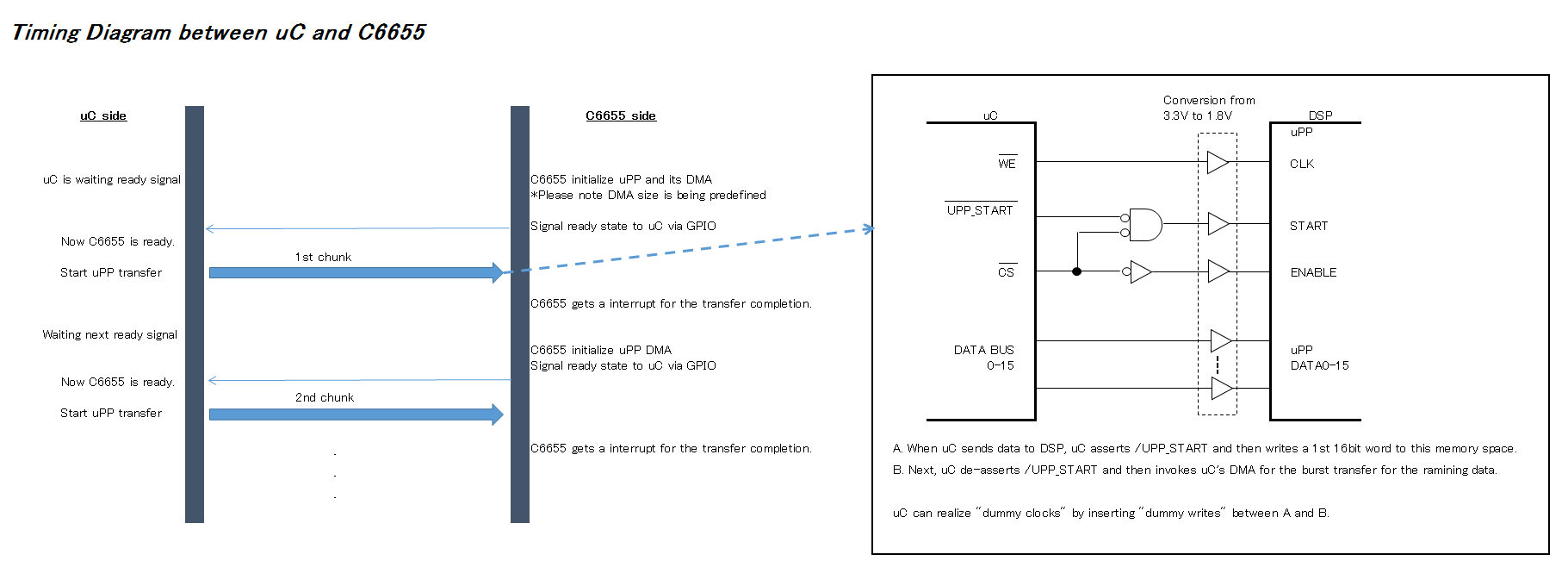

Their system works as below. Please note this is just a test application to verify uPP transport.

1. C6655 setups uPP DMA to receive a single window, which a window is constructed from a single 64byte line.

After configuring uPP DMA, C6655 signals uPP host via GPIO. When incoming data reaches to 64bytes, an interrupt is

generated and C6655 checks the contents of input buffer whether it is expected data or not. And lastly,

C6655 setups uPP DMA for next 64byte reception, and then signals to uPP host via GPIO again.

The system works like this. Please note, cache is being disabled in system.

2. Now uPP host side.

After getting the GPIO notification, uPP host understands C6655 has been completed to configure

uPP DMA to receive 64byte chuck and starts transfer.

The waveform looks like this at the beginning of each 64byte chunk.

As you see, there is no waveform for data lines, but please assume the data lines are always driven

at each START/ENABLE activation and all signals are being latched by CLOCK on rising edge.

Also, please note my customer had been verified that there was no WAIT signal activation during the transfer.

- Yellow : CLOCK

- Green : START

- Magenta : ENABLE

- Blue : WAIT

3. It seems the uPP host is sending each 64byte chunks perfectly.

We don't find any errors in software logic in uPP host side and any AC timing violations in waveform.

However, C6655 misses some 64byte lines !! Here is erroneous scenario:

uPP Host C6655

<1st 64byte chunk> ------------- No interrupt happens. No valid data in receive buffer.

<2nd 64byte chunk> ------------- No interrupt happens. No valid data in receive buffer.

<3rd 64byte chunk> -------------- Transfer completion interrupt happens. <2nd 64byte chunk> is received, rather than <3rd 64byte chunk>

<4th 64byte chunk>------------- No interrupt happens. No valid data in receive buffer.

<5th 64byte chunk>------------- No interrupt happens. No valid data in receive buffer.

<6th 64byte chunk>-------------- Transfer completion interrupt happens. <5th 64byte chunk> is received, rather than <6th 64byte chunk>

1st, 3rd, 4th, and 6th frames are completely missed. Also, 2nd and 5th frames are received and their contents is expected,

but these are "delayed" to the next time frame.

Well, that is our current situation, but we found a workaround -- this looks curious workaround however.

When uPP host intentionally inserts dummy clocks at the end and at the beginning of

each chunk, all chunks are transferred correctly! The workaround looks like this :

uPP Host C6655

<3 dummy clocks ,1st 64byte chunk, 2 dummy clocks> ------------- <1st 64byte chunk> received with correct data

<3 dummy clocks ,2nd 64byte chunk, 2 dummy clocks> ------------- <2nd 64byte chunk> received with correct data

<3 dummy clocks ,3rd 64byte chunk, 2 dummy clocks> ------------- <3rd 64byte chunk> received with correct data

<3 dummy clocks ,4th 64byte chunk, 2 dummy clocks> ------------- <4th 64byte chunk> received with correct data

<3 dummy clocks ,5th 64byte chunk, 2 dummy clocks> ------------- <5th 64byte chunk> received with correct data

<3 dummy clocks, 6th 64byte chunk, 2 dummy clocks> ------------- <6th 64byte chunk> received with correct data

Please let me know your suspicions for the root cause.

I see may posts about uPP transfer problem, but I could not find any validated answers...

Best Regards,

Kawada