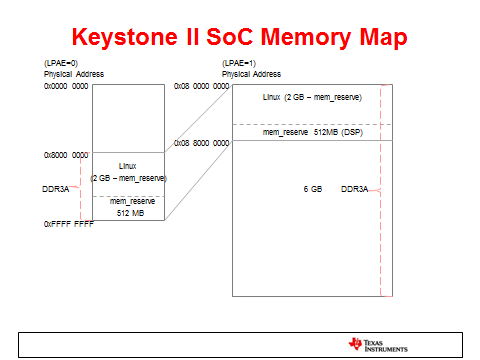

I'm gonna run two applications (ARMv7, C66) on the EVMK2H mounting 4GB RAM.

I don't quiet understand about LPAE.

According to above MCSDK wiki (Using more than 2GB of DDR3A memory),

U-boot creates two memory banks when mem_lpae=1, mem_reserve=512M and ddr3a_size=4 or 8,

but I don't know starting address of DSP side memory.

memory {

reg = <0x00000008 0x00000000 0x00000000 0x60000000

0x00000008 0x80000000 0x00000001 0x80000000>;

};

In this case, ARM Linux uses 1.5GB of first 2GB bank.

At this time, what is the range of address that DSP can access?

I don't know a meaning of this.

The second bank represent the remaining memory.

That memory starts at the fixed address and size equal "ddr3a_size - 2".

What I ultimately want is to split DDR3A memory independently,

and to utilize known memory except ARM occupied for running DSP application on 4GB RAM.

Gilbert.