Hi,

I am trying to implement SRIO_LoopbackTestProject (pdk_C6670_1_1_2_6\packages\ti\drv\exampleProjects\SRIO_LoopbackTestProject) in board to board scenario.

Board Setup:

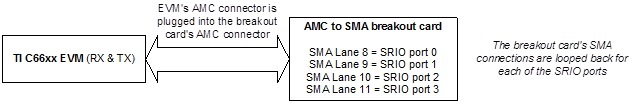

EVM6670LE Board A --> TI LC Dual EVM Breakout card --> EVM6670LE Board B

I want to send data from EVM board A and do line loopback on EVM board B to transmit the received data.

For this I changed the code in device_srio_loopback.c file to put the EVM A in normal mode as shown below and loaded the .out file in EVM A.

/* Configure SRIO ports to operate in loopback mode.

CSL_SRIO_SetLoopbackMode(hSrio, 0);

CSL_SRIO_SetLoopbackMode(hSrio, 1);

CSL_SRIO_SetLoopbackMode(hSrio, 2);

CSL_SRIO_SetLoopbackMode(hSrio, 3); */

/* Configure SRIO to operate in Normal mode. */

CSL_SRIO_SetNormalMode (hSrio,0);

CSL_SRIO_SetNormalMode (hSrio,1);

CSL_SRIO_SetNormalMode (hSrio,2);

CSL_SRIO_SetNormalMode (hSrio,3);

I have problem in configuring the EVM B in line loopback mode.

1. How do I put the EVM in line loopback mode. Is it just enabling the LLB bit in PLM_SP(n)_IMP_SPEC_CTL register as shown below ?

// Bypass the tx clock crossing the FIFO

implControl.lineLoopbackMode = 1;

CSL_SRIO_SetPLMPortImplSpecificControl (hSrio, 0, &implControl);

CSL_SRIO_SetPLMPortImplSpecificControl (hSrio, 1, &implControl);

CSL_SRIO_SetPLMPortImplSpecificControl (hSrio, 2, &implControl);

CSL_SRIO_SetPLMPortImplSpecificControl (hSrio, 3, &implControl); */

2. Do I need to do anything else other than adding the above code in the device_srio_loopback.c file to get the .out file for EVM board B ? I mean do I need to remove any part of the code that was in project for Board A (Data transfer code or initialization code) ?

Can someone help me with this.

Thanks

Hari