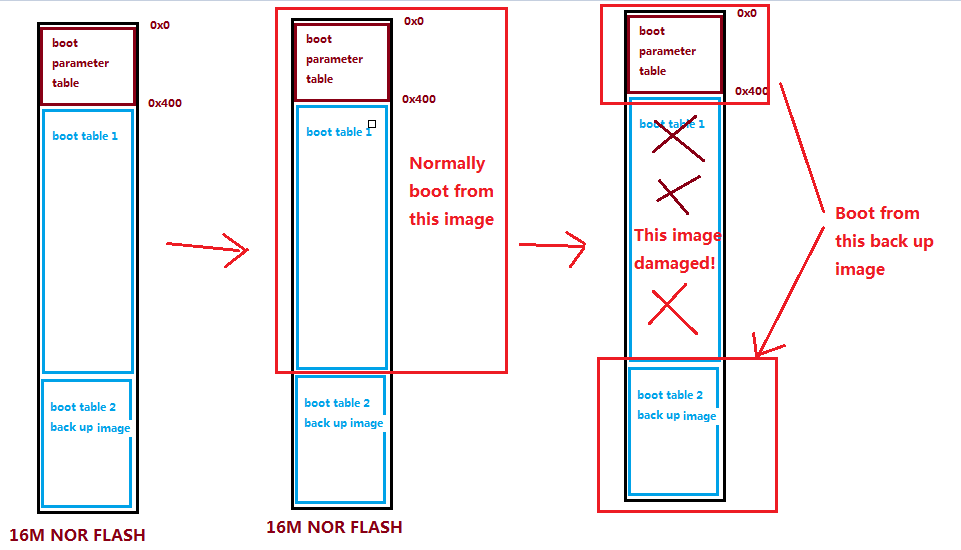

We want to implement a double image solution when use SPI boot, in case one image damaged we can also boot from another image.

1. Now i can sucessfully boot in the SPI boot mode,for a NOR flash.

2.The NOR FLASH is 16M capacity, now my normal image is about 5MB.

3.In some cases,when the customers update the FLASH image, the image may have some prombles,the image maybe damaged and can't boot then.

4.so we want to have another backup image burnt into the NOR FLASH, in the last 5M NOR flash space.

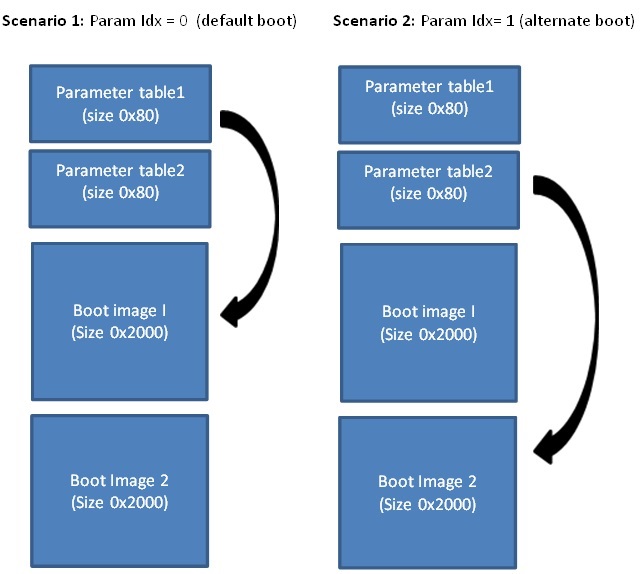

5. when the first image is in the front 5MB is damaged and the the DSP can not boot,then we can change the the boot GPIO pin states(conresponse to DEVSTAT-BOOT MODE) to config another boot parameter table to boot from another NOR FLASH address,where we have burned a backup image into,then the DSP can boot again.

In my understanding, i have to append another paramter table into the image,and the paramter table must indicate to the other Boot table address instead of 0x400,am i right?

but I don't know how to use the utilities to make all those works.

1.How to append another parameter table,which indicate another boot address?

2.How to build the other backup image?should I keep the first 0x400 as the boot parameter space also?

Give me an example,please, because the TI bootloader documents said nothing!