Hi All,

I am trying to run the TSIP_testProject on C6678 EVM evaluation board using CCS 5.2.

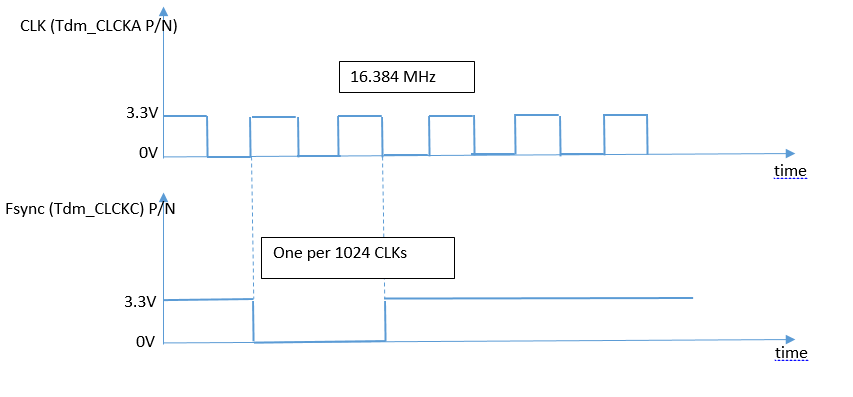

I don't have an AMC chassis so I amusing my own generator to supply CLK to TDM_CLCA P/N and Fsync to TDM_CLKC P/N through the AMC connector. The signal timing diagram is shown below. The CLC is 16.384MHz and Fsync has an active low level and the active level length of 1.5 clock periods. Fsync repeats every 1024 clock periods. Before running the TSIP_testProject I have verified that the differential clock and Fsync are present at the input of the level shift circuitry (FPGA). The TSIP_testProject I am using is located at ..\pdk_C6678_1_1_2_5\packages\ti\drv\tsip\...

Unfortunately the test fails with various results with the typical output also shown at the end of this post.

So my questions are:

1. Are the signals I supply to the C6678 EVM have the correct parameters like polarity, shift between clock and Fsyns, the correct number of clock periods between Fsync etc.

2. Do I need to make extra connections on the AMC and/or I need to supply some another signals?

Thank you,

[C66xx_0] **************************************************

[C66xx_0] ********** TSIP Test Start ***********************

[C66xx_0] **************************************************

[C66xx_0] Verify TSIP Port 0 data transfer...

[C66xx_0] -->Slot 0 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 17 samples.

[C66xx_0] tsipToAppBuf[40]=0x0 when it should have been 0x41

[C66xx_0] -->Slot 1 TSIP data transfer verfication failed. Array tsipToAppBuffer is empty.

[C66xx_0] -->Slot 2 TSIP data transfer verfication failed. Array tsipToAppBuffer is empty.

[C66xx_0] -->Slot 3 TSIP data transfer verfication failed. Array tsipToAppBuffer is empty.

[C66xx_0] -->Slot 4 TSIP data transfer verfication failed. Array tsipToAppBuffer is empty.

[C66xx_0] -->Slot 5 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[26]=0x0 when it should have been 0x33

[C66xx_0] -->Slot 6 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[26]=0x0 when it should have been 0x33

[C66xx_0] -->Slot 7 TSIP data transfer verfication failed. Array tsipToAppBuffer is empty.

[C66xx_0] -->Slot 8 TSIP data transfer verfication failed. Array tsipToAppBuffer is empty.

[C66xx_0] -->Slot 9 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[26]=0x0 when it should have been 0x33

[C66xx_0] -->Slot 10 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[26]=0x0 when it should have been 0x33

[C66xx_0] -->Slot 11 TSIP data transfer verfication failed. Array tsipToAppBuffer is empty.

[C66xx_0] -->Slot 12 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[103]=0x0 when it should have been 0x81

[C66xx_0] -->Slot 13 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[26]=0x0 when it should have been 0x33

[C66xx_0] -->Slot 14 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[26]=0x0 when it should have been 0x33

[C66xx_0] -->Slot 15 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[110]=0x0 when it should have been 0x85

[C66xx_0] -->Slot 16 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[110]=0x0 when it should have been 0x85

[C66xx_0] -->Slot 17 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[29]=0x0 when it should have been 0x36

[C66xx_0] -->Slot 18 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[29]=0x0 when it should have been 0x36

[C66xx_0] -->Slot 19 TSIP data transfer verfication failed. Array tsipToAppBuffer is empty.

[C66xx_0] -->Slot 20 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[236]=0x0 when it should have been 0x4

[C66xx_0] -->Slot 21 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[29]=0x0 when it should have been 0x36

[C66xx_0] -->Slot 22 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[29]=0x0 when it should have been 0x36

[C66xx_0] -->Slot 23 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[236]=0x0 when it should have been 0x4

[C66xx_0] -->Slot 24 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[35]=0x0 when it should have been 0x3c

[C66xx_0] -->Slot 25 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[35]=0x0 when it should have been 0x3c

[C66xx_0] -->Slot 26 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[35]=0x0 when it should have been 0x3c

[C66xx_0] -->Slot 27 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[236]=0x0 when it should have been 0x4

[C66xx_0] -->Slot 28 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[236]=0x0 when it should have been 0x4

[C66xx_0] -->Slot 29 TSIP data transfer verfication failed.

[C66xx_0] Before failing, verified 1 samples.

[C66xx_0] tsipToAppBuf[106]=0x0 when it should have been 0x81

[C66xx_0] -->Slot 30 TSIP data transfer verfication failed. Array tsipToAppBuffer is empty.

[C66xx_0] -->Slot 31 TSIP data transfer verfication failed. Array tsipToAppBuffer is empty.

[C66xx_0] TSIP Port 0 data transfer verfication FAILED

[C66xx_0] TSIP Test ended. Test Failed.