Hi,anyone :

I have one broad on which there are one chip of C6670 DSP woking as REC equipment and one chip of altera FPGA (belonging to Cyclone V GT falimy) woking as RE equipment .The CPRI Bus is used to transfer data between each .

The project running in the DSP chip is downloaded from TI Web called" AIF2 LTE TDD" ,

and within the FPGA , one serdes module as the physical layer + CPRI protocol module ( designed privately accordding to <CPRI_v_4_1_2009-02-18>,not IP Core) as logic layer .

During the test , i ( FPGA engineer ) found that , at FPGA ponit, link is built and and keep on , the anto-negotiate function is also done (local proticol parameter such as Ethernet Point and Protocol Version is changed by DSP ,not the initial value anymore), and also radio / hyperframe/basic frame can be received and anylised by the private CPRI protocol module . But the payload is null .

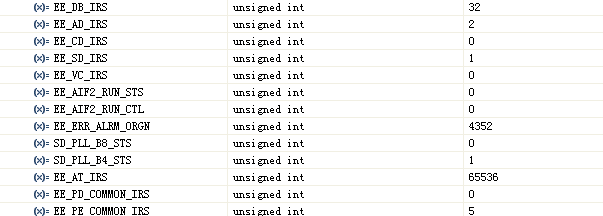

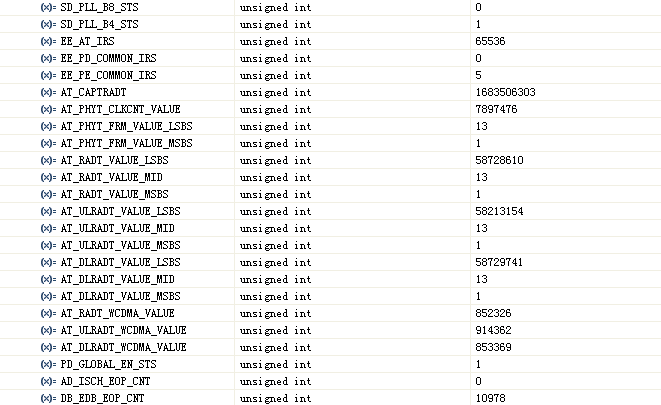

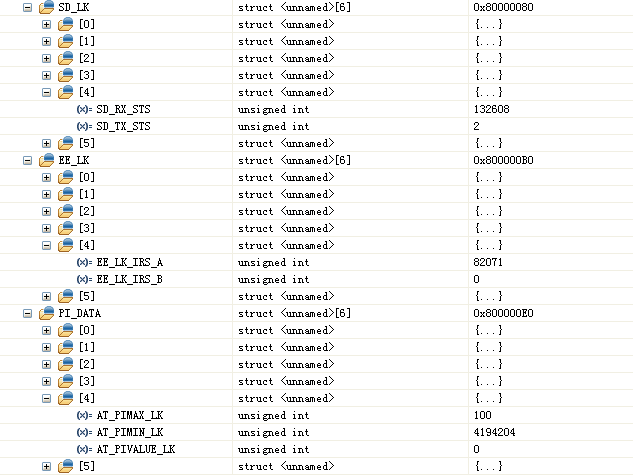

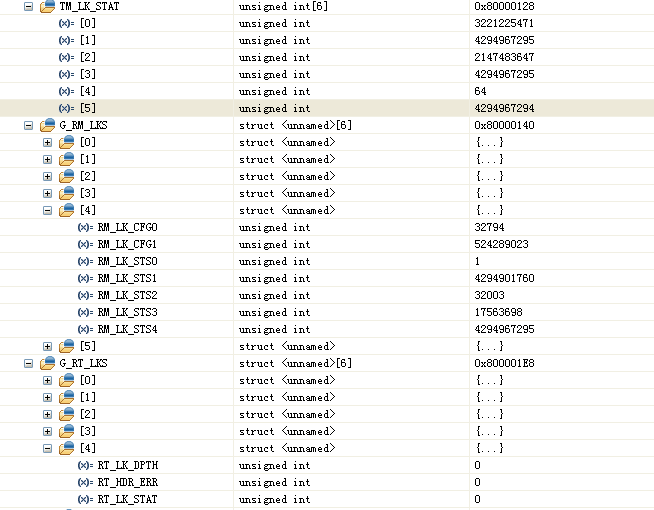

at the DSP point , link is up ,RM/TM is in SYN state , no payload is received .

Can anyone give me some suggestion about this ?

that is all ,thanks a lot !

Rick