Hi,

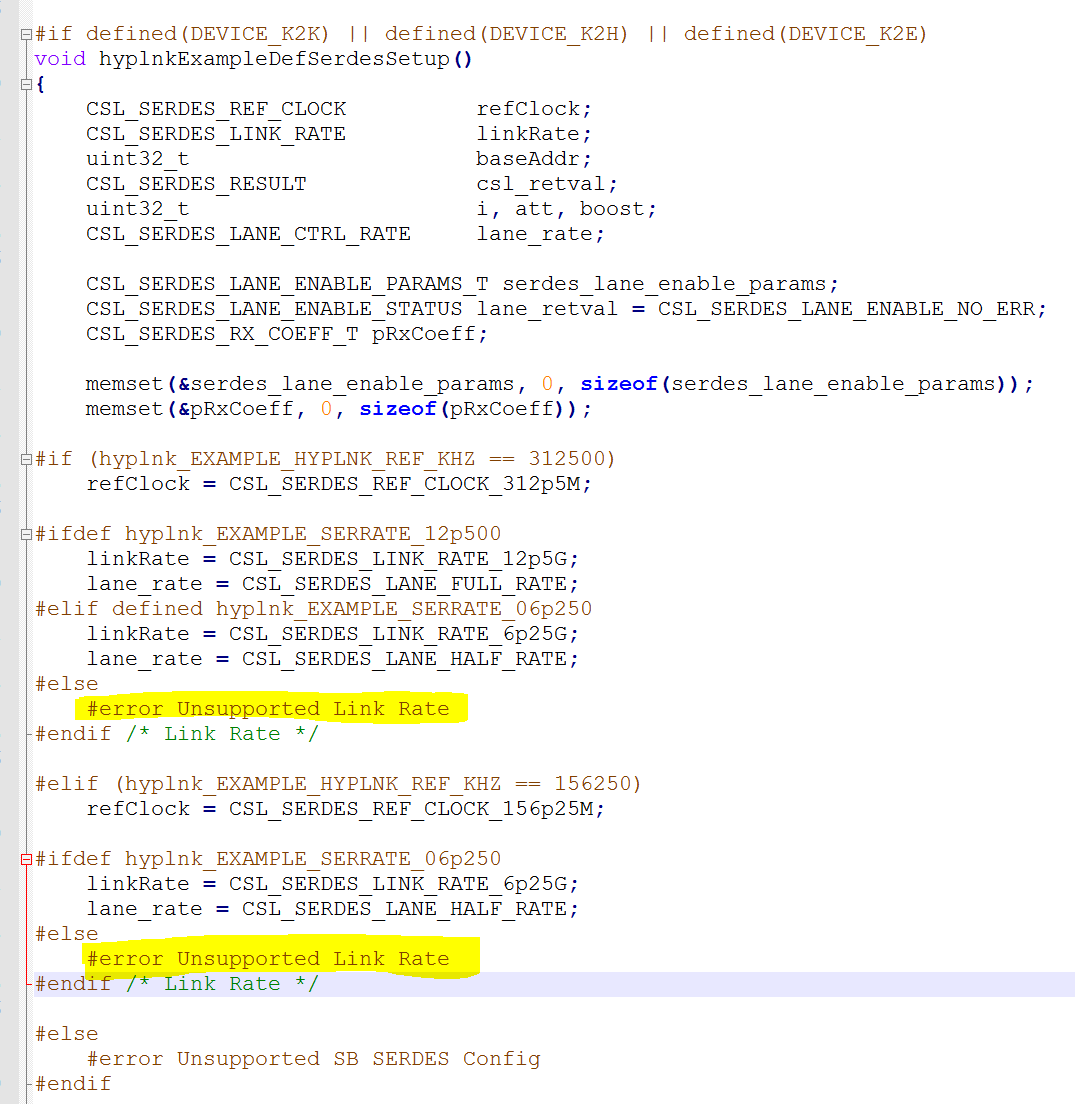

We are using hyperlink interface to 6.25g and would like to move to 10G however both pdk_keystone2_3_01_03_06 and pdk_keystone2_3_01_04_07 10G do not support this mode for 312.5MHz reference clock.

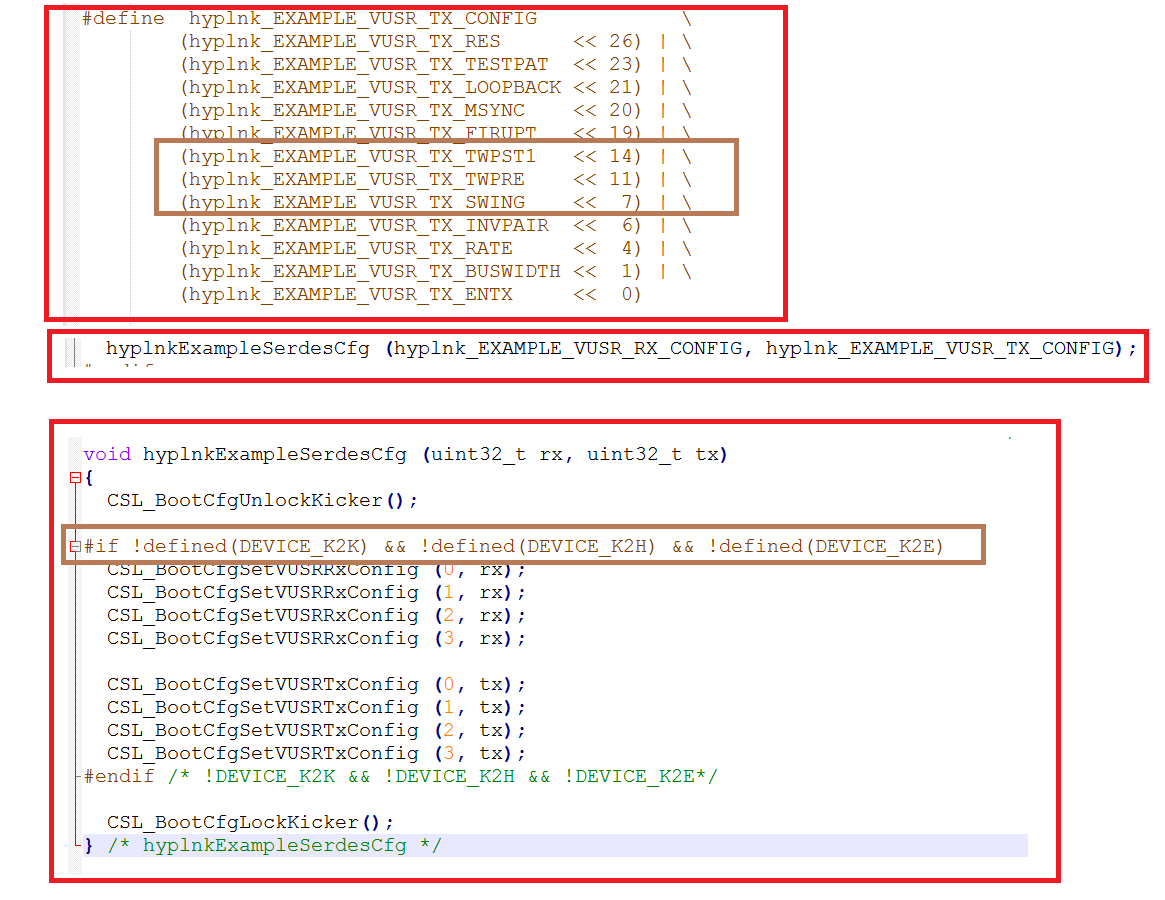

See attached screenshot taken from "C:\ti\pdk_keystone2_3_01_03_06\packages\ti\drv\hyplnk\example\common\hyplnkLLDIFace.c" for your reference.

Errata sheet for K2K/K2H does not reflect 10G issue.

Could you please confirm why this is unsupported?

Kind Regards,

Piyush