Hi,

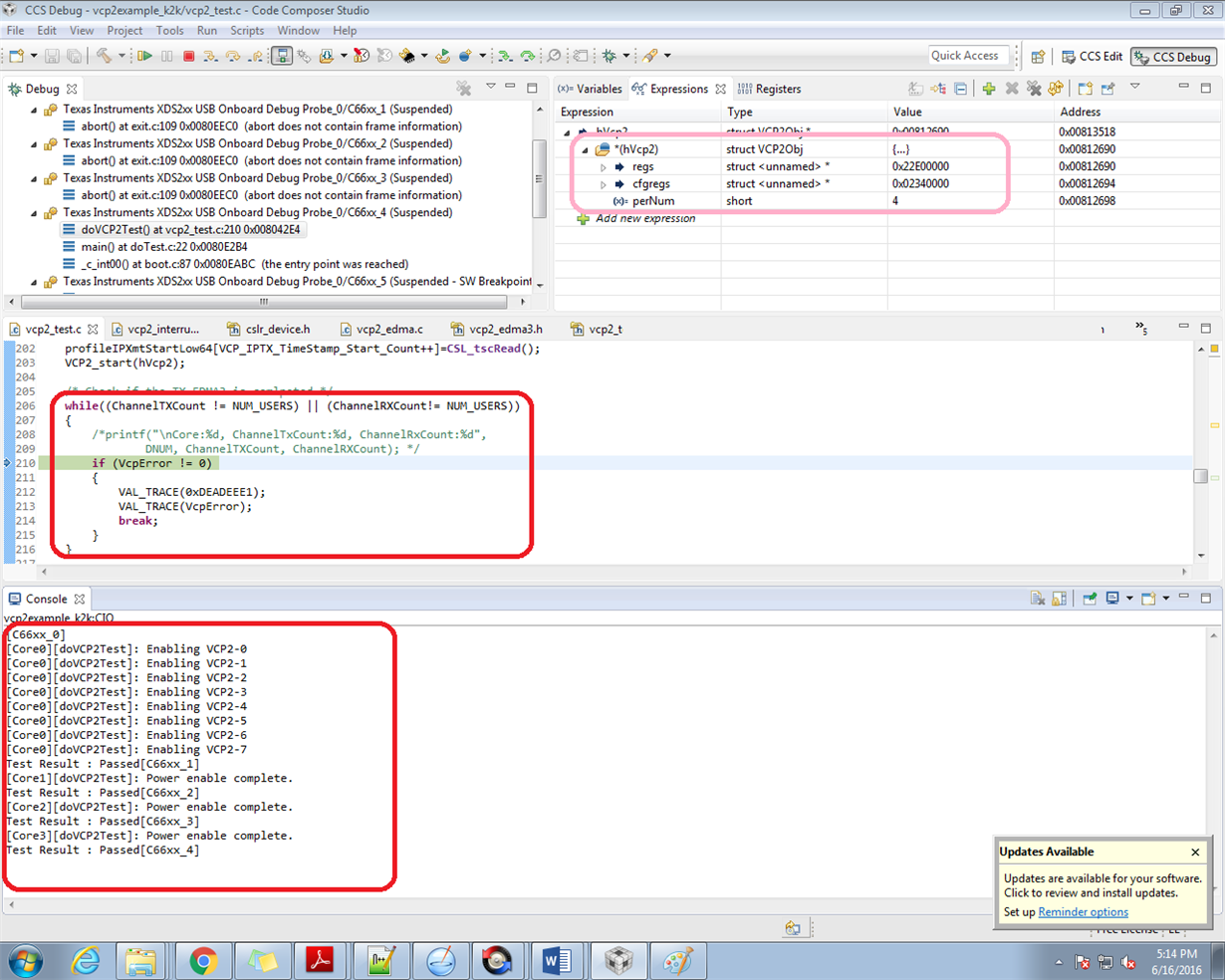

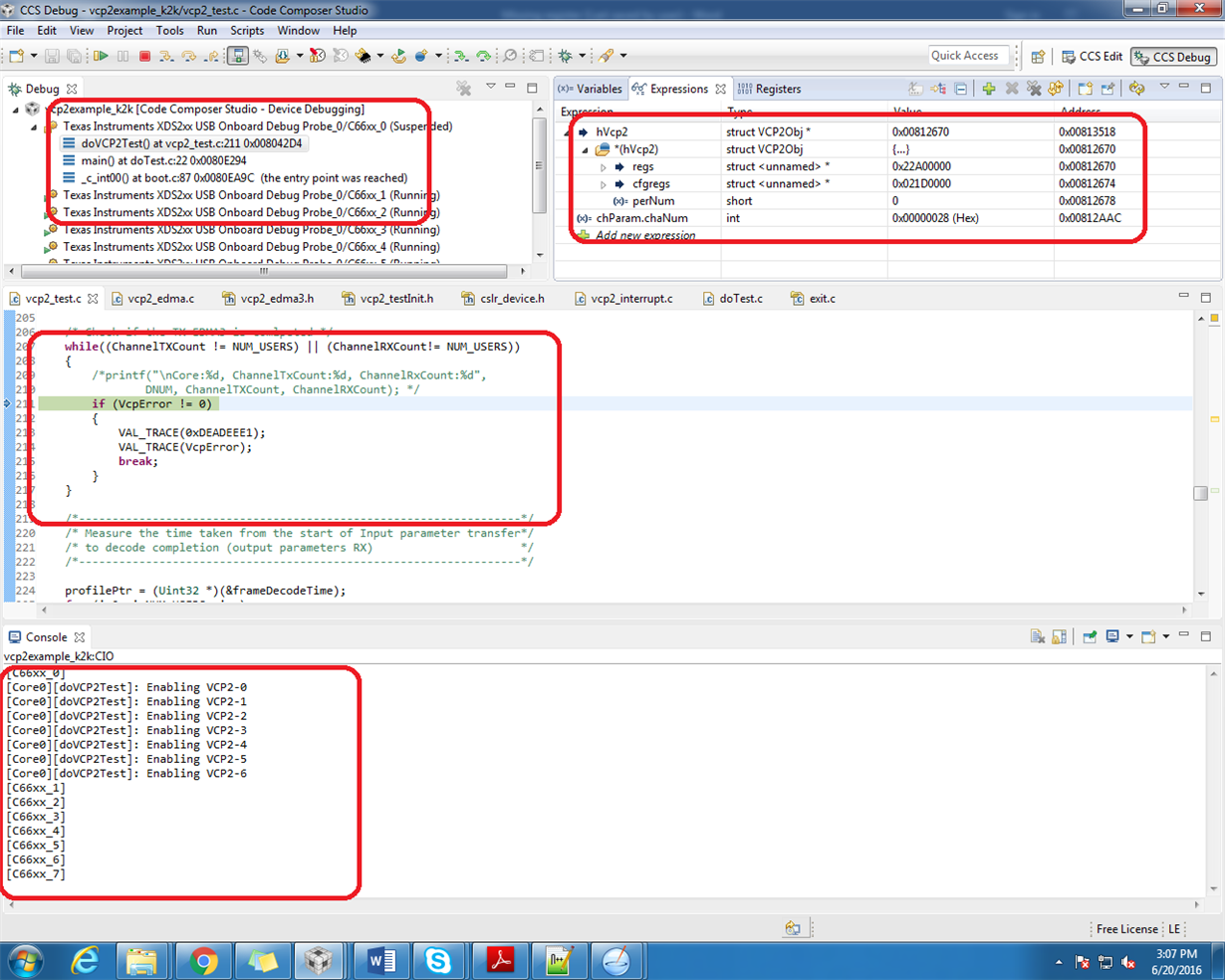

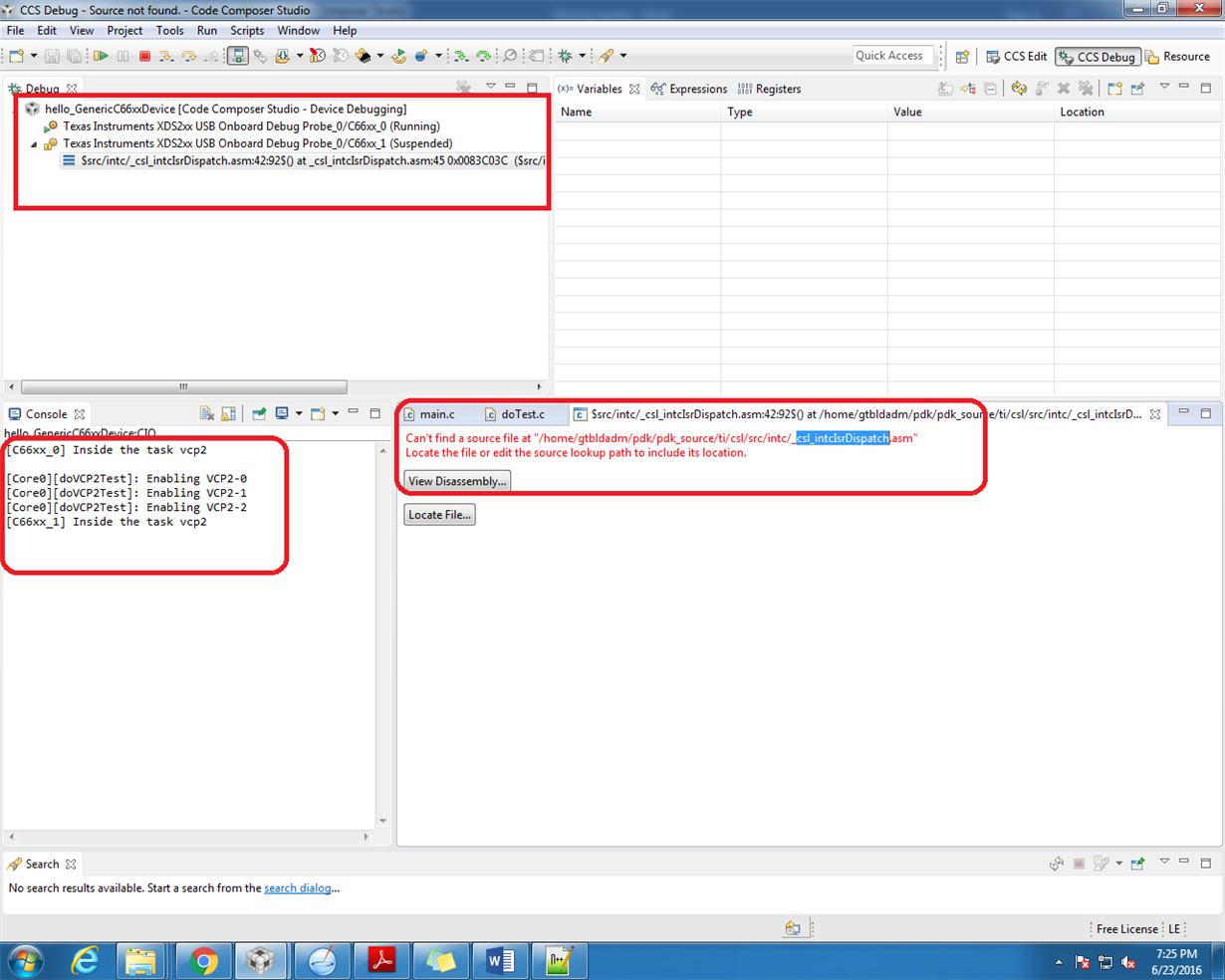

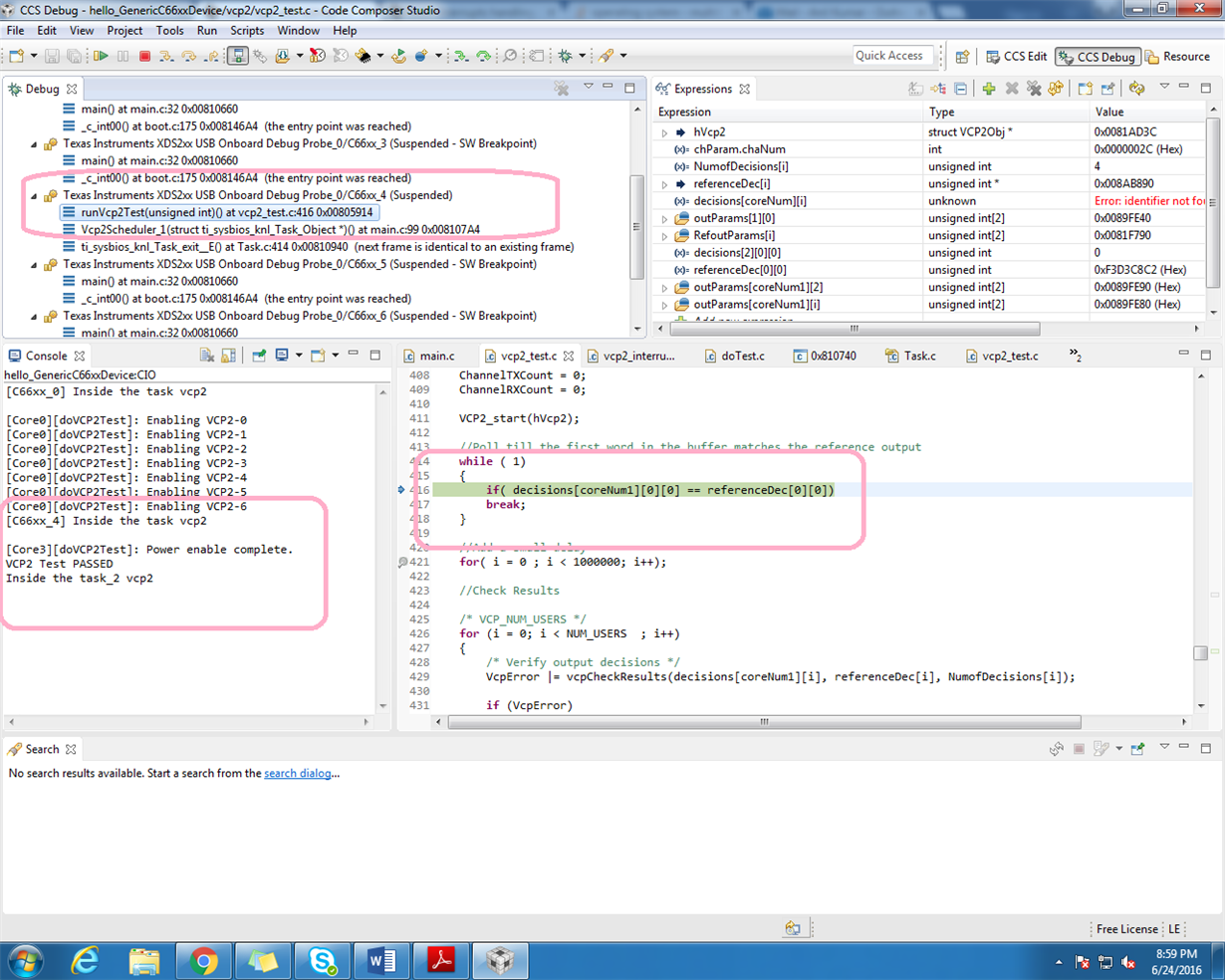

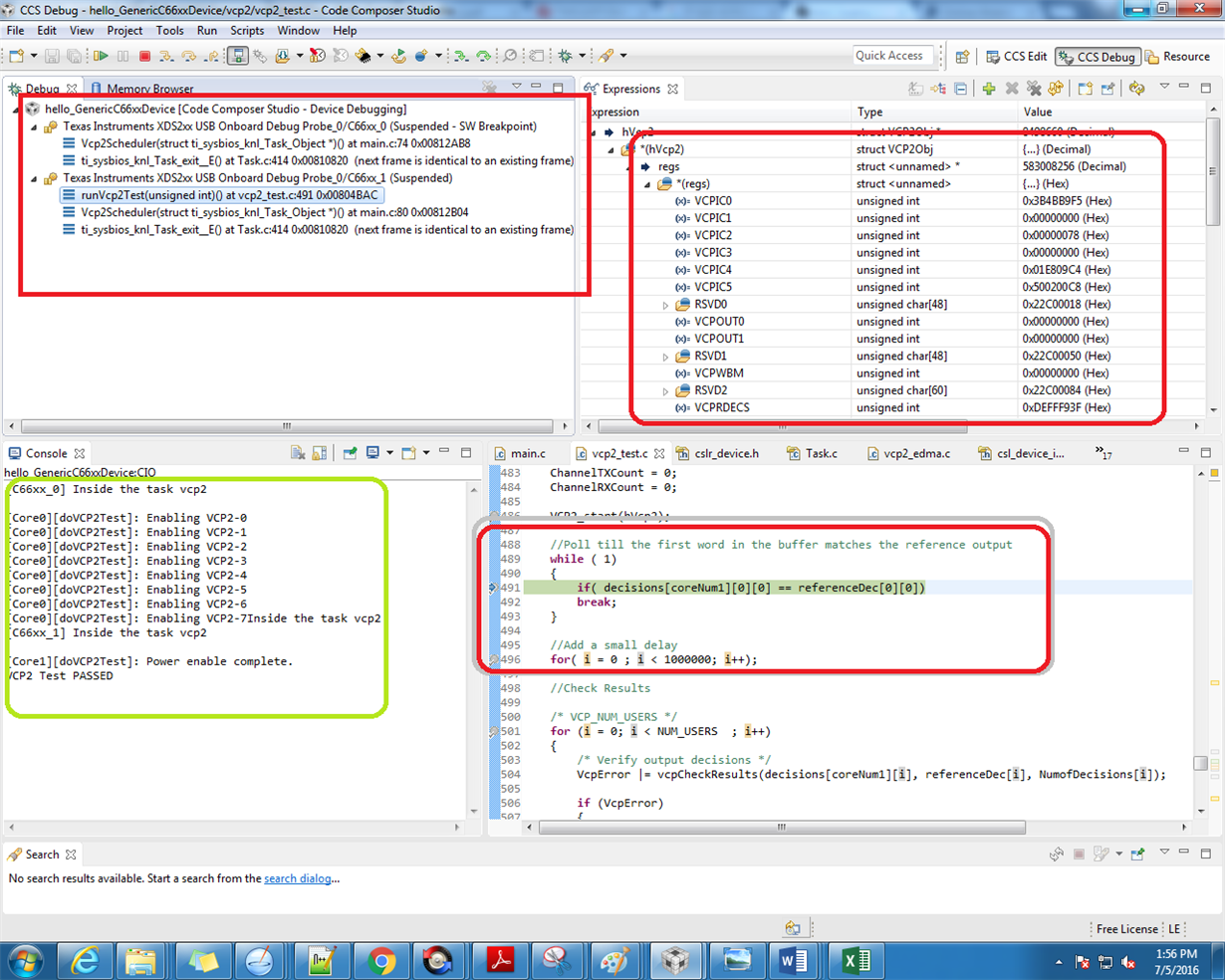

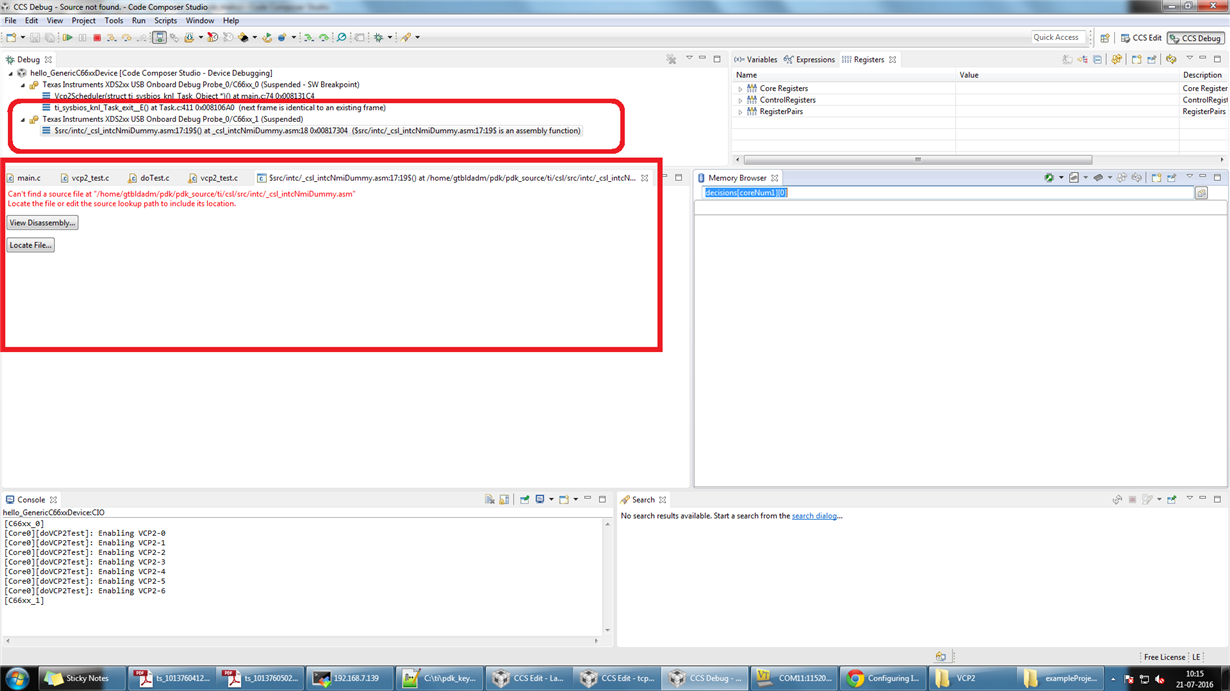

My application need vcp2 support on 6638 platfrom. I am building an application based on 6657 example. The code configures edma channels and vcp2.. I had hard time aligning the csl definition for 6638. I have create a version that buids with my project. But when trying on the 6638 platform i dont get vcp2 result.

Please have a look at the attached and help me,

Regards

anilVCP.7z