Hi,

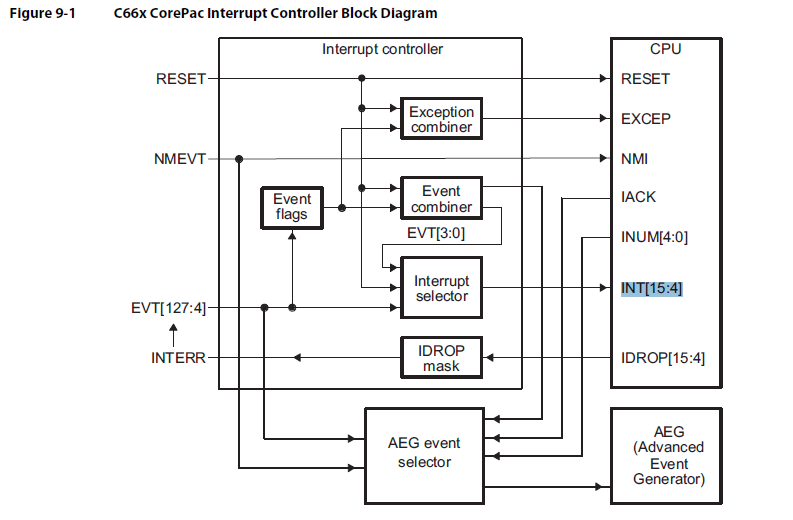

I'm working on interrupts in c6678 processor.

The below is the code for Pcie interrupts.

{

int eventId;

ti_sysbios_family_c64p_Hwi_Params params;

CpIntc_mapSysIntToHostInt(0, 50, 32);

CpIntc_enableHostInt(0, 32);

CpIntc_enableSysInt(0, 50);

eventId = CpIntc_getEventId(32);

Hwi_Params_init(¶ms);

params.arg = 32;

params.eventId = eventId;

params.enableInt = TRUE;

Hwi_create(4, &hwi_pcie_inta, ¶ms, NULL);

Hwi_enableInterrupt(4);

Hwi_enable();

}

1. How to choose the system interrupt and host interrupt numbers?

2. What does 0, 50 and 32 represents here in the above code in CpIntc_mapSysIntToHostInt() and how the numbers are choosen?

3. What does number 4 represents in the Hwi_create() function?

Thanks, Waiting for the reply.