Hi,

I would like to know about the output and ODT impedance setting of DDR3 I/F on C6678.

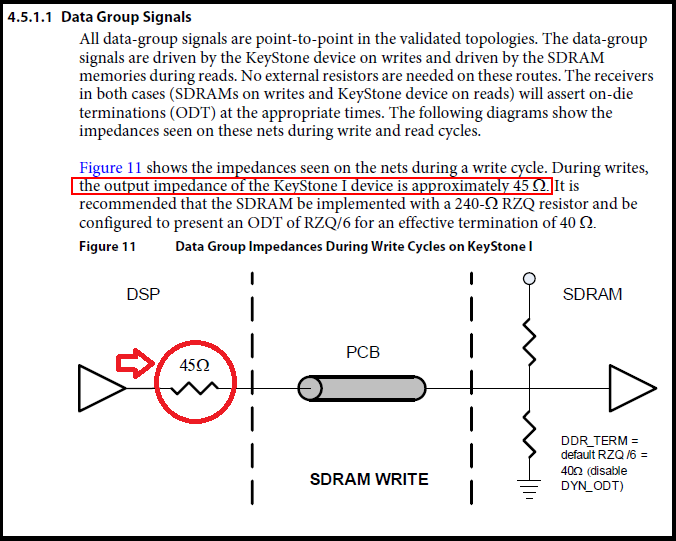

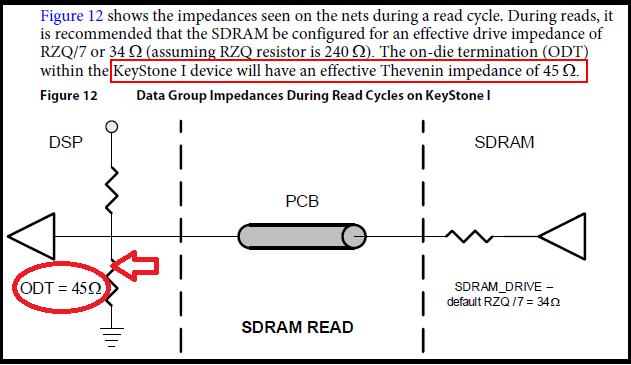

Q1: it seems that DDR3 Design Requirements for KeyStone Devices" is described the output and ODT impedance is 45ohm, but can I change these values? If so, please tell me the register information to change.

Q2: I am using the IBIS model(sprm537) for DDR3 simulation. I would like to simulate the output impedance setting with 40 ohms and the ODT setting with 50 ohms. Because the IBIS model included these parameters. If I can't change the output and ODT impedance of the C6678, please tell me why the IBIS model contains parameters other than 45 ohms.

Best regards,

H.U