hi TI professors,

I am using the altera fpga pcie communication with c6678 and the fpga work as EP and the dsp work as RC.I wanner realize the function is that the fpga control ad converter to acquisition data and save data to fifo. When fifo full will trigger the MSI which interrupt vector is 0, the dsp core0 receive the interrupt and remote configuration the fpga dma registers to transfer data from fpga fifo to dsp ddr3 sdram. When the dma trigger the dma transfer finished MSI which interrupt vector is 1, the dsp core0 receive the msi interrupt and notify core1 to process data.

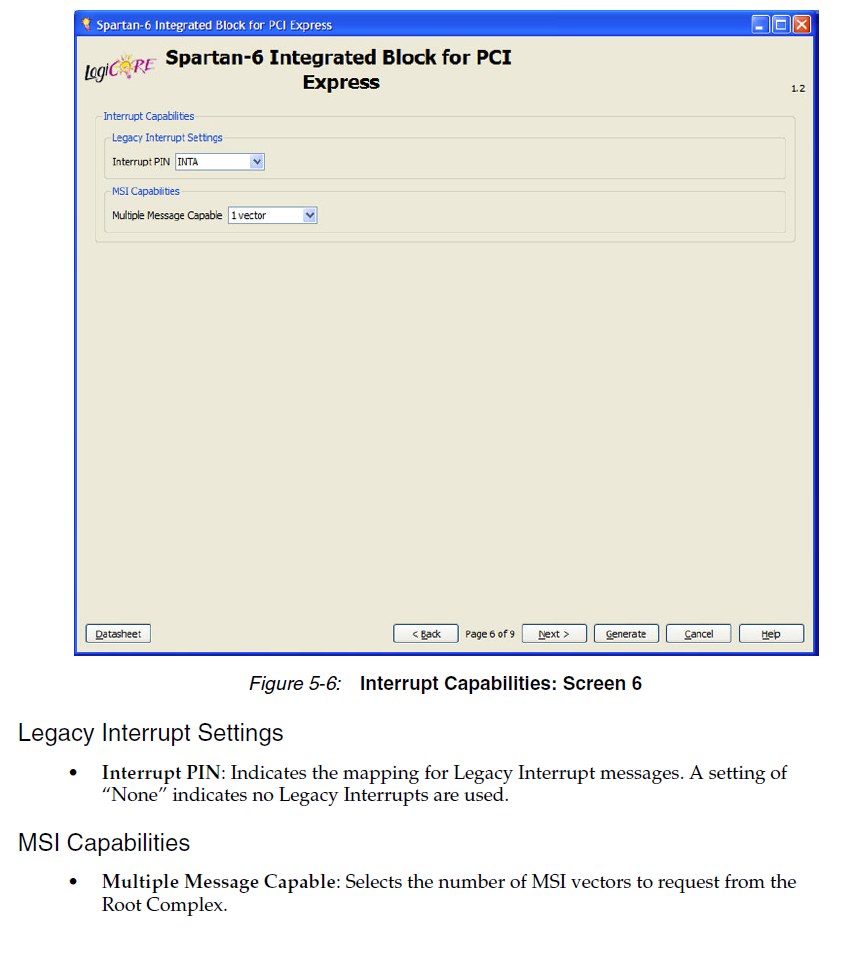

Now my problem is the fpga will trigger two msi interrupt which interrupt vector are 0 and 1, core0 receive two msi interrupt but show common interrupt vector.I look the PCIE specification datasheet and I find the MSI vector must continue and msi-x interrupt vector can discontinue.But the dsp core0 just receive msi vector is 0,8,16 and 24.It meaning is that fpga cannot send two msi interrupt to dsp.

I am not sure if I am understanding this right. Can u give me some idea about dsp core0 receive two msi from fpga?

think u!