I have couple of queries on the EVM module design.

1. TLV1117-33CDCY used to generate VCC3V3_MP_ALT.Here Vin is 12V. But as per the datasheet of the TLV1117 part, Vin has to be 4.75 V to 10 V for a 3.3V output. can someone clarify ?

2. 3.3V – VDD33 (1A? it is mentioned as TBD in EVM) powering the DVDD of the SOC is generated using UCD7242 device and VCC3V3_Aux (2.57A) – used by other peripherals is generated using TPS54620 device. Is there any reason to generate separately? Is it just for isolation?

3. 0.75V generated using LDOàI see 2 ICs used to generate 0.75V for DIMMs and Discrete ICs. Total current consumption on VTT(including DIMM and Discrete ICs) would not exceed 3A in total. Do we really need to have two ICs to generate the same?

4. 1.5V for DDR- consumption is 6A (3A for DIMM + 3A For DDR IC), But why is it designed for 12A?

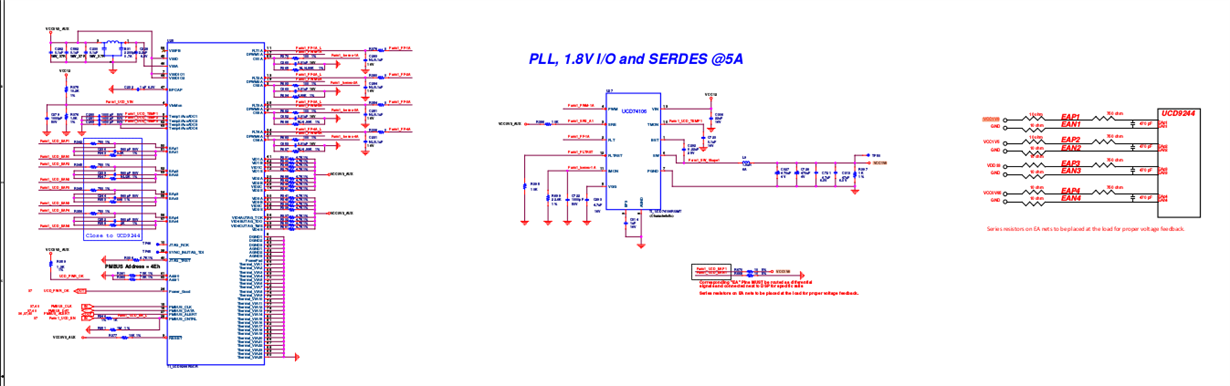

5. How is the loop compensation controlled for the PWM controller(UCD9244) + Power stage (UCD74120)?

6. UCD7242- output inductor is chosen to be 0.47uF (17.5A) while the requirement is 5A. Is there any reason for it?

7. UCD74120 sourcing the CVDD DSP+ARM coreà How is the output inductor decided? What is the inductor ripple current? Also the output is a variable voltage between 1.8V to 1V- how is this controlled/ programmed?