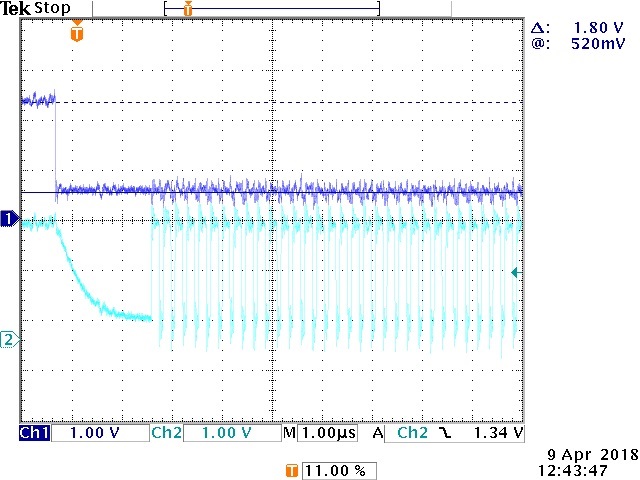

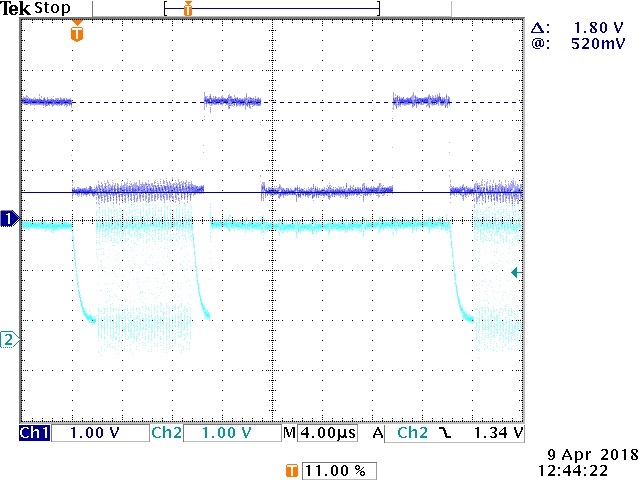

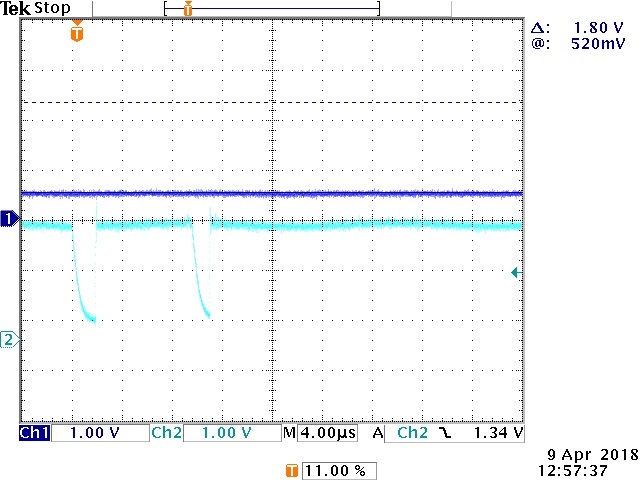

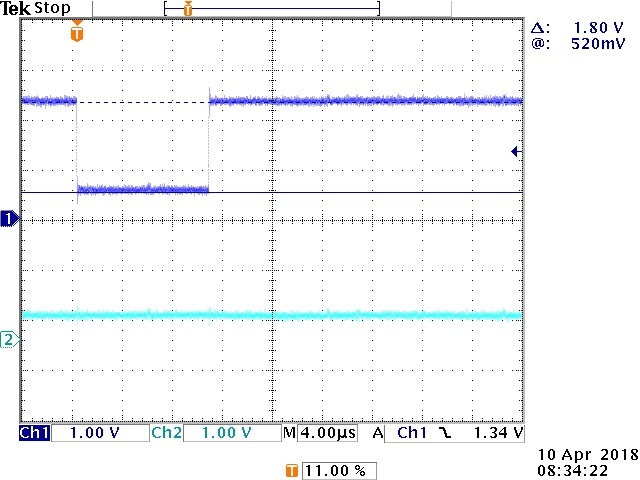

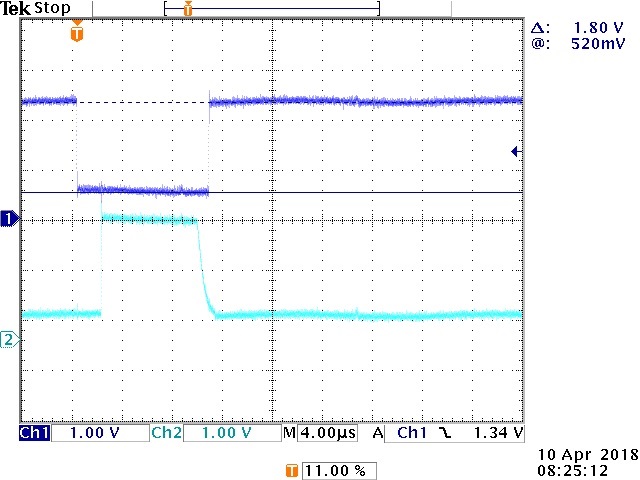

Hi, in our design, I am interfacing to a parallel NOR Flash (PC28F512P30EFA) via the EMIF16 bus. I can read the status register, however, when I go to do anything with the device ID or mfg ID, The Databus coming back from the part is oscillating with a pattern. The period is about 250ns. I've tracked it down to bit A23 oscillating at this rate during the read cycle. Only happens when I issue a 0x90 Read ID command prior to reading, Doesn't happen when I read flash or the status register. Program and Erase commands do not work.

The Board is routed incorrectly, with A23 going to Pin A25 on the Part, and not acting as bit 1. However, I wouldn't expect it to do this. Any Thoughts?

Brian Gonzales