Tool/software: TI-RTOS

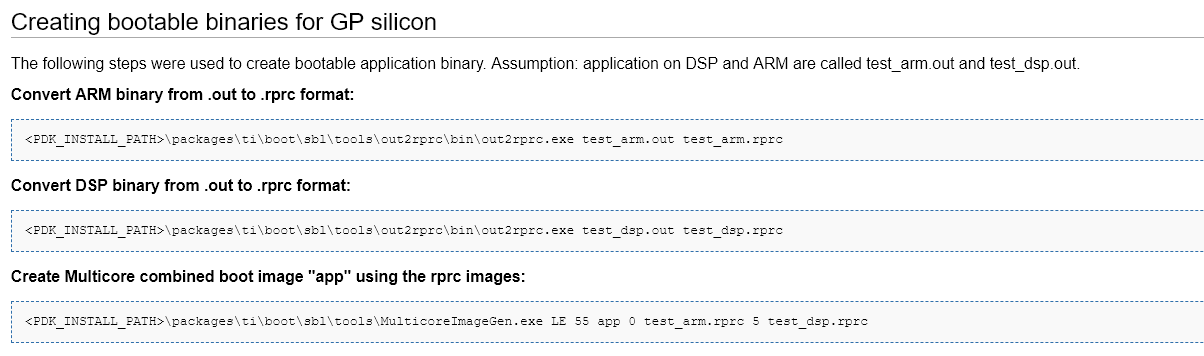

We are using K2GEVM(66AK2G02) which is connected to daughter card. As of now we are booting the board by flashing the test_dsp.out and test_arm.out through ccs. We are using "processor_sdk_audio_1_00_00_06". Now I wanted to boot the board in standalone mode, without loading the firmware(test_dsp.out and test_arm.out) every time from CCS. It would be helpful if some one can point me to the pointer to get this done.