Tool/software: TI-RTOS

Hello!

I have a system where C6670 communicates with Spartan 6 FPGA over PCIe. We use MSI to make interrupts to DSP.

The system was in use for several years already being pretty stable. However, recently we face some issue with MSI, which is hard to trace. Under certain circumstances, when there is intensive PCIe traffic it looks like PCIe subsystem fails to trigger interrupt. I monitor MSI0_IRQ* registers and see:

(*0x21800100) 0x0000000C (*0x21800104) 0x00000004 (*0x21800108) 0x00000005 (*0x2180010c) 0x00000005

So according to MSI0_IRQ_ENABLE_SET (0x21800108) bits 1 and 2 are enabled, that is MSI vectors 8 and 16. According to both MSI0_IRQ_STATUS (0x21800104) and MSI0_IRQ_STATUS_RAW (0x21800100) bit 2 (i.e. 0x4) is pending. However, interrupt is not triggered. For the matter of experiment, I have cleared bit 2 by writing 4 to 0x21800104, then retriggered it by writing 16 to MSI_IRQ (0x21800054). I see the bit of interest gets cleared, then asserted again, but interrupt does not occur.

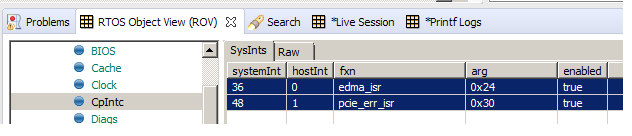

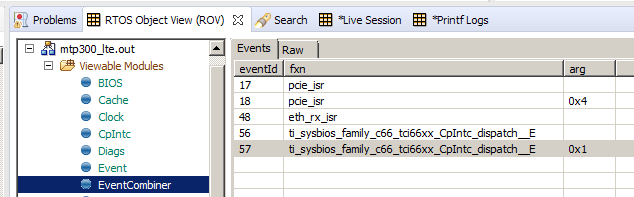

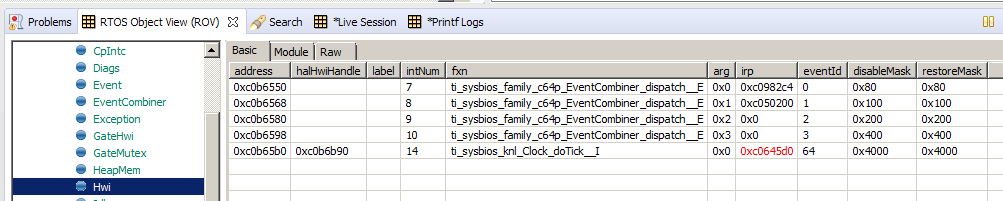

MSIs are routed through EventCombiner, relevant piece of config looks as:

EventCombiner.eventGroupHwiNum[0] = 7; EventCombiner.eventGroupHwiNum[1] = 8; EventCombiner.eventGroupHwiNum[2] = 9; EventCombiner.eventGroupHwiNum[3] = 10; EventCombiner.events[17].fxn = '&pcie_isr'; EventCombiner.events[17].arg = 0; EventCombiner.events[17].unmask = false; EventCombiner.events[18].fxn = '&pcie_isr'; EventCombiner.events[18].arg = 4; EventCombiner.events[18].unmask = false;

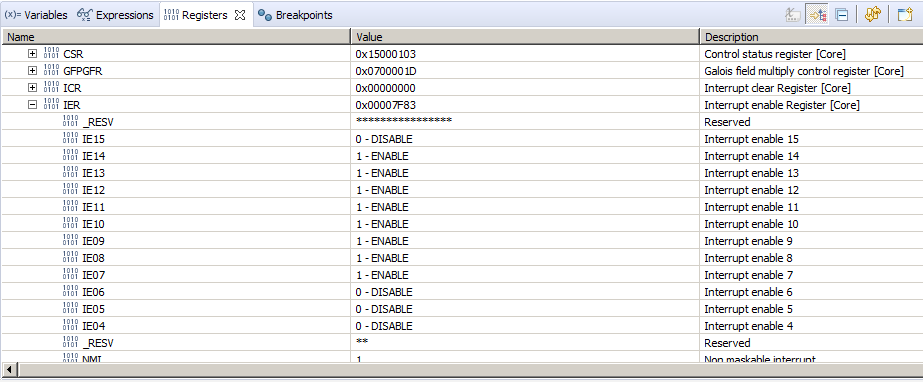

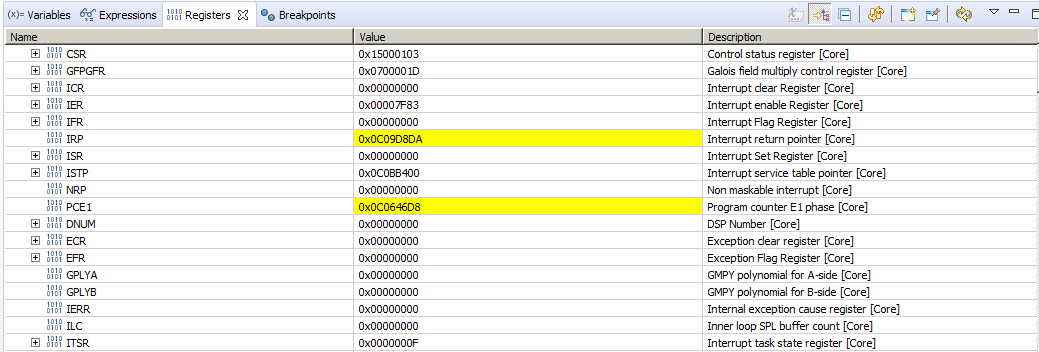

They both get enabled in runtime and operational for sure. The point is that MSI vector 16 stops triggering after certain activity. I have checked what looks relevant to me:

Still I could not find what could be a reason for MSI ISR to be not triggered.

Please advise what else should I check.

Thanks