Tool/software: TI-RTOS

Hi,

66AK2H14 is interfaced to Altera MAX10 series CPLD through EMIF16 interface.

EMIF16 is configured to Select Strobe Mode.We have to perform CPLD read/write through EMIF16.

I have posted one query about how to configure control lines of EMIF. here is the link of my previous post

I have to write 4096 bytes of data from the position 0000 to 4095.

I am writing to EMIF as ,

#define CPLD_DATA_ADDR 0x0034000000

data_addr = ( uint16_t *)CPLD_DATA_ADDR;

/* 8-bit flash */

while(i++ < SIZE)

{

if(j==256)

j=0;

*data_addr = cmp_val[j++];

data_addr++;

}

as per the previous post , The address lines are carried though from the lower address bits of the memory map with the shift.

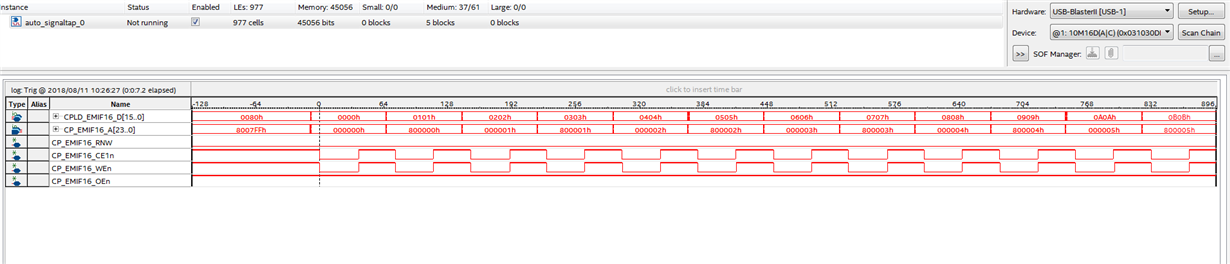

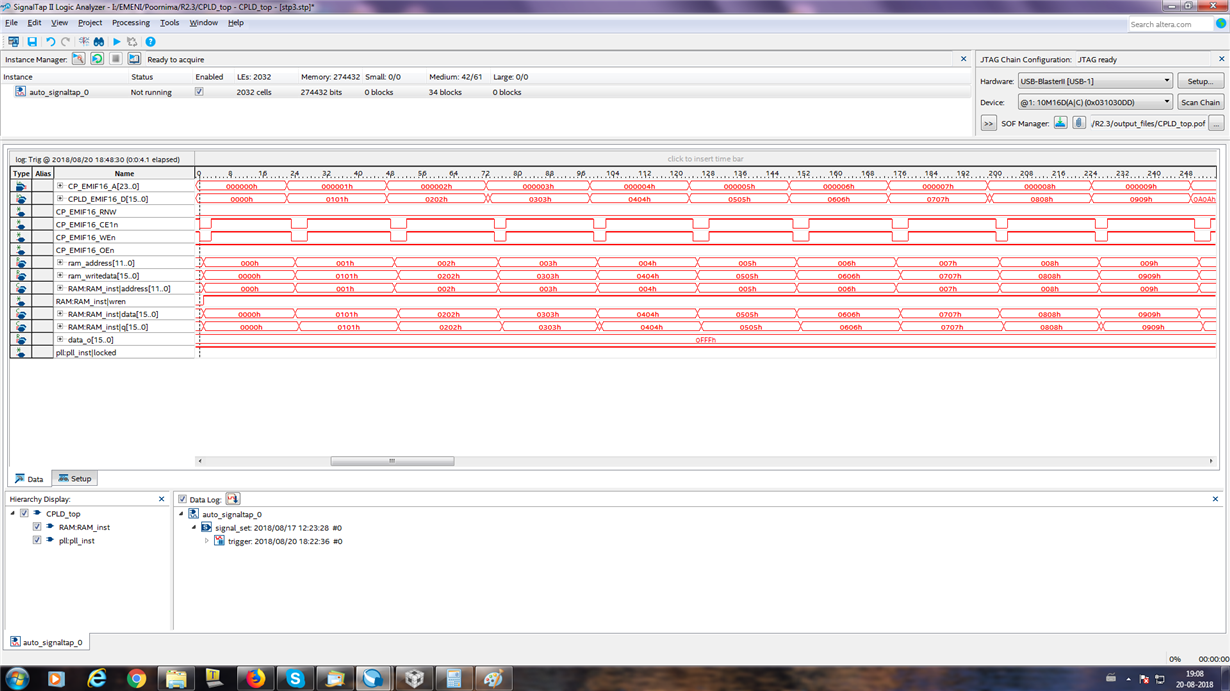

When I signal tap the address line which goes to CPLD I am getting address like 000000 , 800000 , 000001 etc which I have to right rotate to get the correct address.

I have attached the screenshot for your reference.

My doubt is Whether this rotation has to be done by the master(66ak2h14) while writing to 0x34000000 or by the slave(CPLD)?