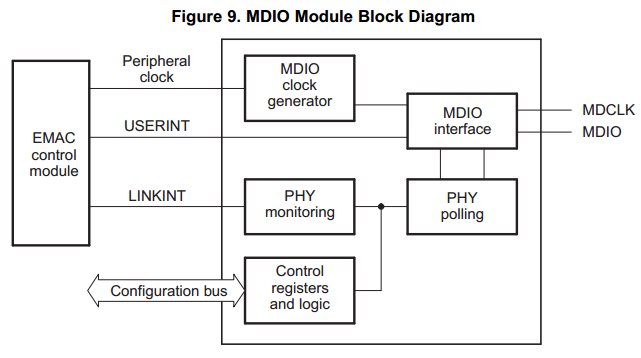

Our customer wants to access the registers of ethernet switch device via the MDIO interface. The registers are not the standard PHY registers. It need two accesses continuously via the standard MDIO protocol. However the two accesses can be disturbed by the PHY Monitoring.

Can the MDIO interface be used to access the registers? Is there the way to prevent the PHY Monitoring during the two accesses?

Best regards,

Daisuke