Hello,

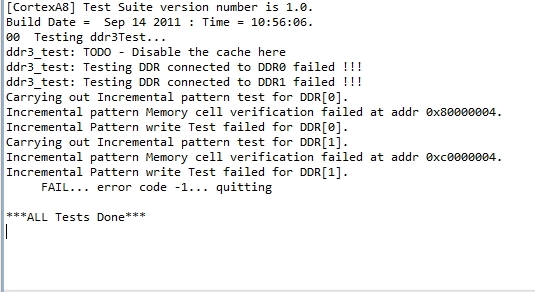

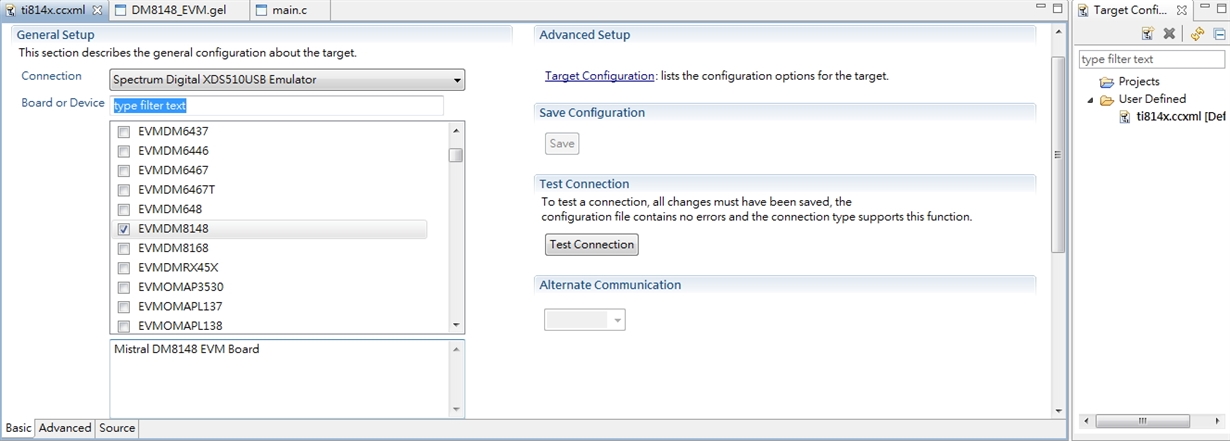

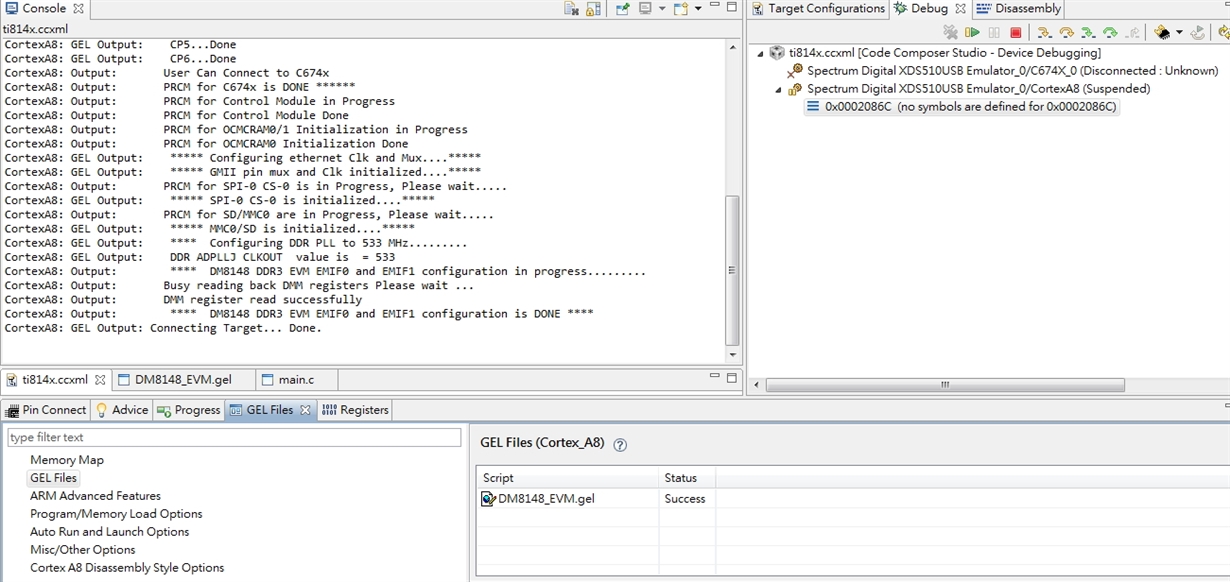

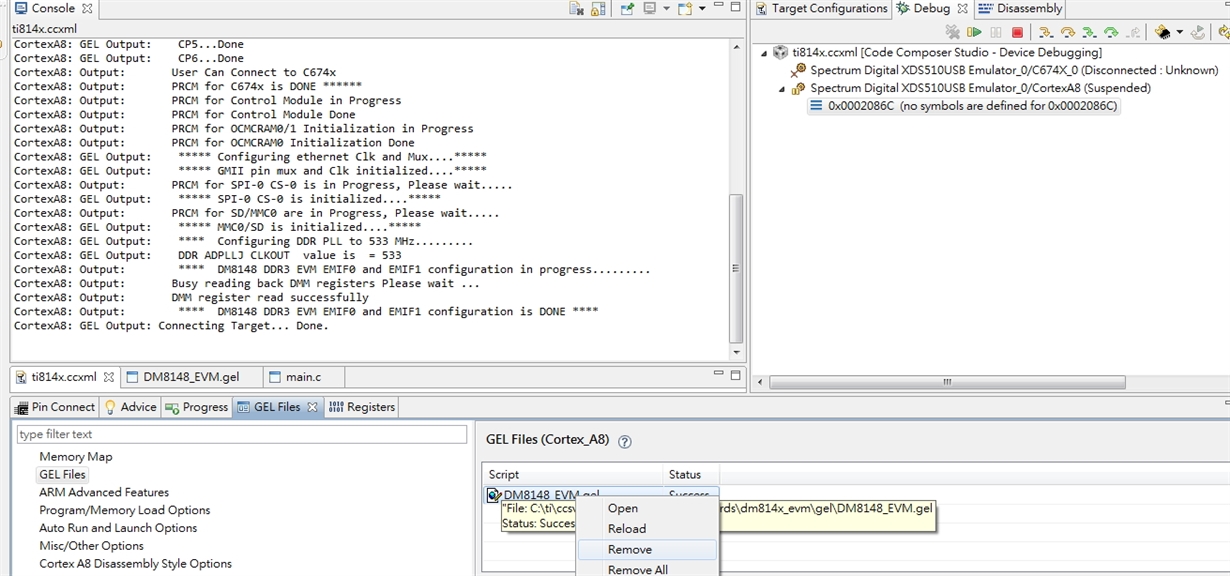

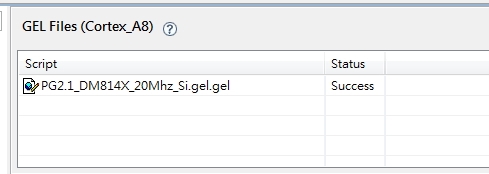

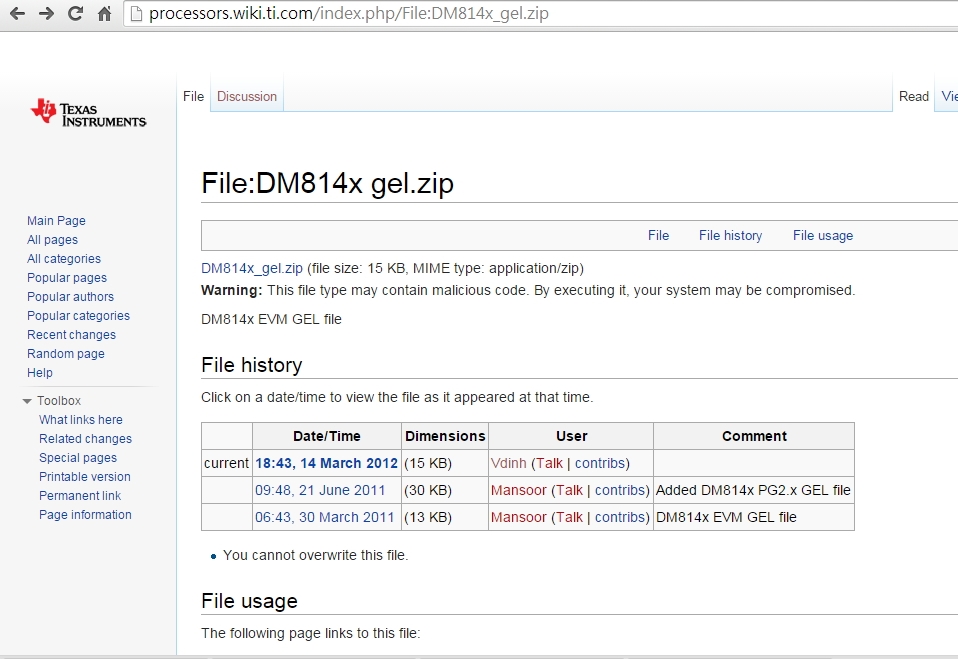

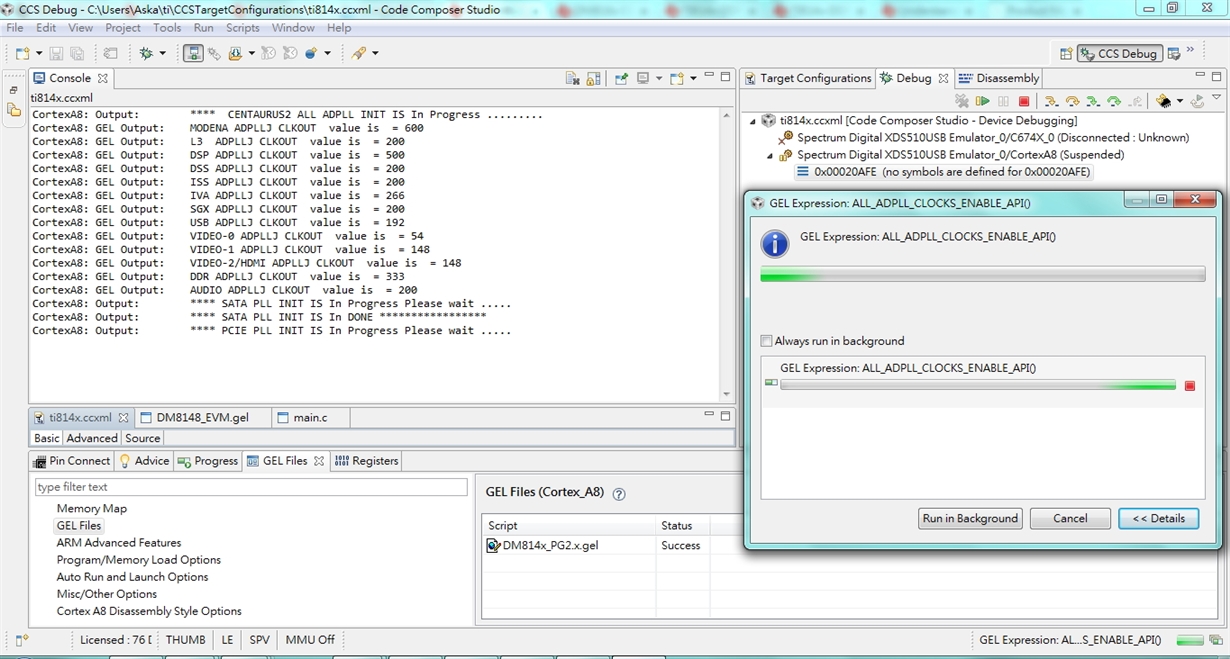

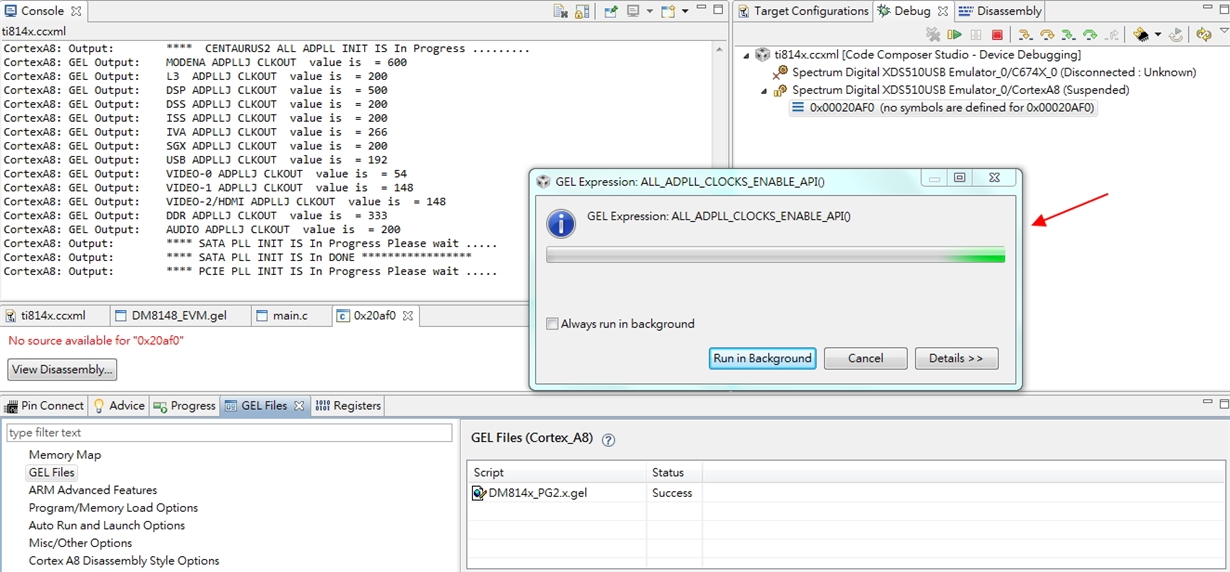

Making DM8148 PCB, there has been a few bad pcb, when the boot mode using Nand flash output without any message, when uart mode can output ccccc ...., but all of the output voltage, reset signal, the oscillator output frequency outputs normal, so can connect using Jtag and ccs to debug it?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.