Hello,

On recording mcasp2 input (using arecord), and then playback the recorded file in PC, we've noticed that it speed is faster.

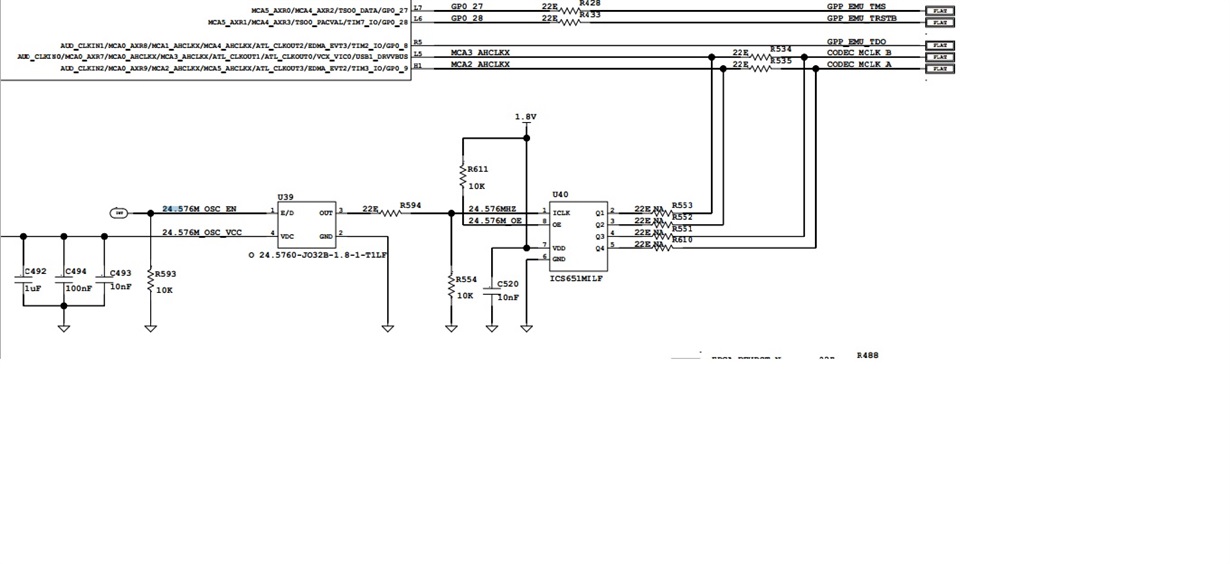

We use external oscillator 24.576Mhz which is conneced to DM8148.

With the help of the below links, I understand that u-boot configures this MCLK clock in clocks_ti814xx.c

#define AUDIO_N 19

#define AUDIO_M 500

#define AUDIO_M2 2

#define AUDIO_CLKCTRL 0x801

I also see that the formula is:

M/(N+1) * CLKINP * 1/M2

I therefore tried to change it as following:

#define AUDIO_N 0

#define AUDIO_M 1

#define AUDIO_M2 1

(in order to ger '1' factor), but then u-boot (minimal) hangs.

I also tried to understand how it works with evm, but it still does not make sense to me:

1. evm hw uses 22.579MHz osscilator, and the code shows:

#define AUDIO_N 19

#define AUDIO_M 500

#define AUDIO_M2 2

#define AUDIO_CLKCTRL 0x801

trying this with the formula I get:

freq = M/(N+1) * CLKINP * 1/M2 = 500/20*22.579M*(1/2) = 282.2375M ,

while I expected to get 24.576M , becuase this is what I see in evm code:

static int ti81xx_evm_hw_params(struct snd_pcm_substream *substream,

struct snd_pcm_hw_params *params)

{....

/* default */

sysclk = 24576000;

}

Is there anything wrong in the above assumptions ?

Regards,

Ran