Hi,

We have a custom board where the DM8107 is meant to be outputting 2-channel CCIR656 YCbCr out of DVO1. We know that things are basically functioning, because we also have the HDMI ouput available through the board, and we can see video (though discolored) through that port when our application is running. We have also verified that the registers in the HDVPSS/HDVENC are set up to be in this format:

root@8107:~# readmem 0x48106000

Value at address 0x48106000 (0x4010d000): 0x44013051

We have also verified that all pinmux settings are correct, though we are only using vout[1]_G_Y_YC[2..9] and vout[1]_B_CB_C[2..9] plus vout1 clock, vsync and hsync as our output.

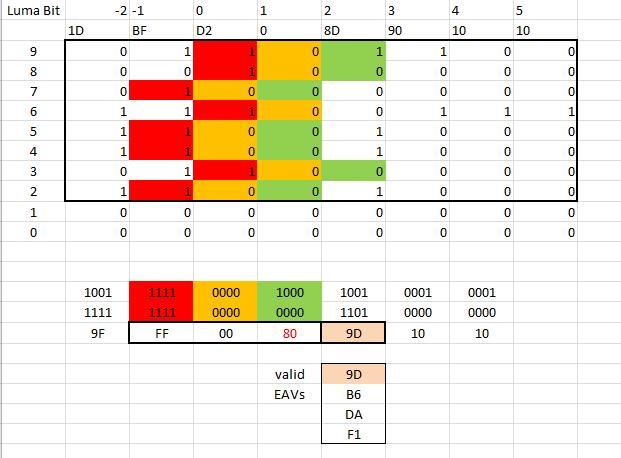

The basic setup is to have these ports going into an FPGA, where we were able to capture the output:

The problem seems to be that, as seen in the logic analyzer capture, certain bits are not being set correctly in the sync words. Are there any known issues that might be related to this, especially on DVO1? We do have other boards that use DVO2, and they work without issue.