Hello

Using DM 814x to capture interlaced video source. Our Requirement is V4l2 should merge both the top and bottom field and deliver single frame. We are trying to use

below is the IOCTL command we use in V4l2 driver in the function ti81xxvin_vps_create().

storageparams.chNum = 0;

storageparams.bufferFmt = FVID2_BUF_FMT_FRAME;

storageparams.fieldMerged = 1;

ret = (inst->captctrl->control(inst->captctrl,

IOCTL_VPS_CAPT_SET_STORAGE_FMT,

(void *)&storageparams, NULL));

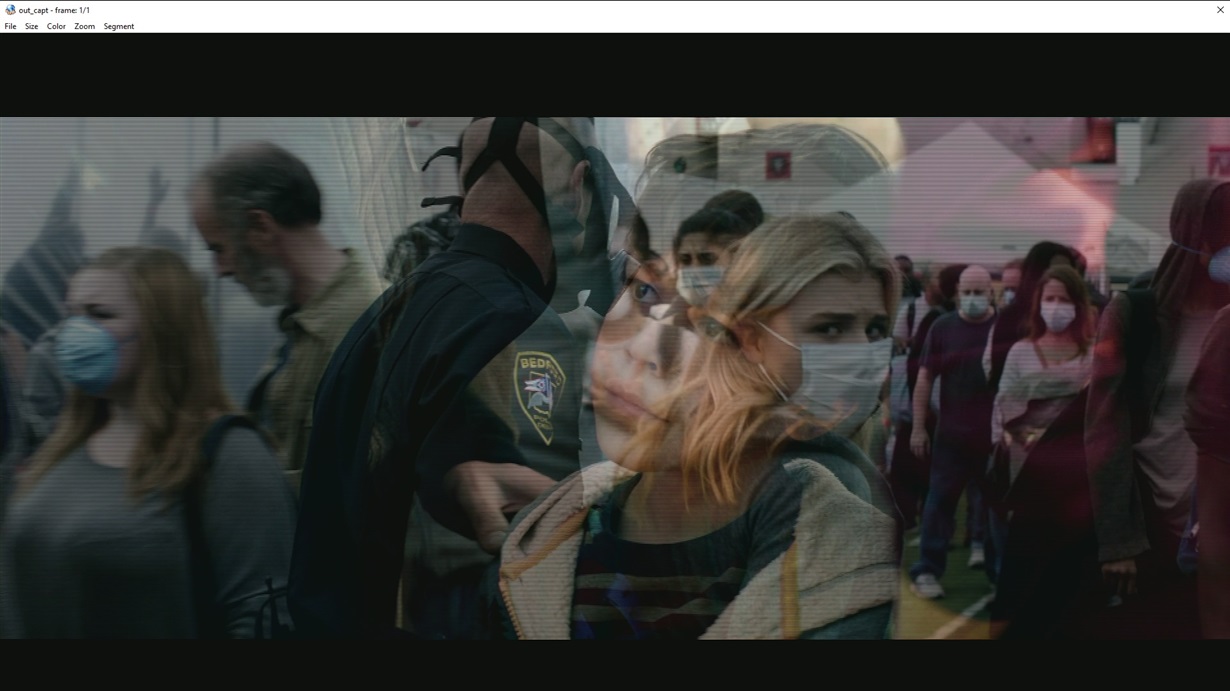

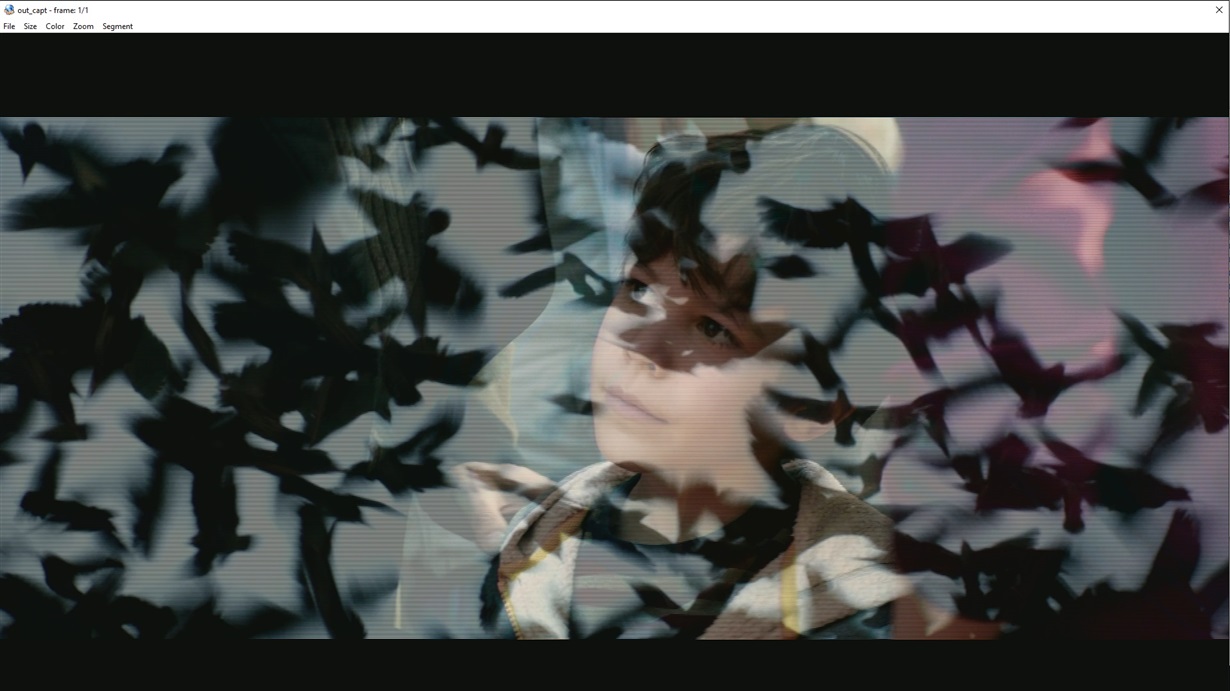

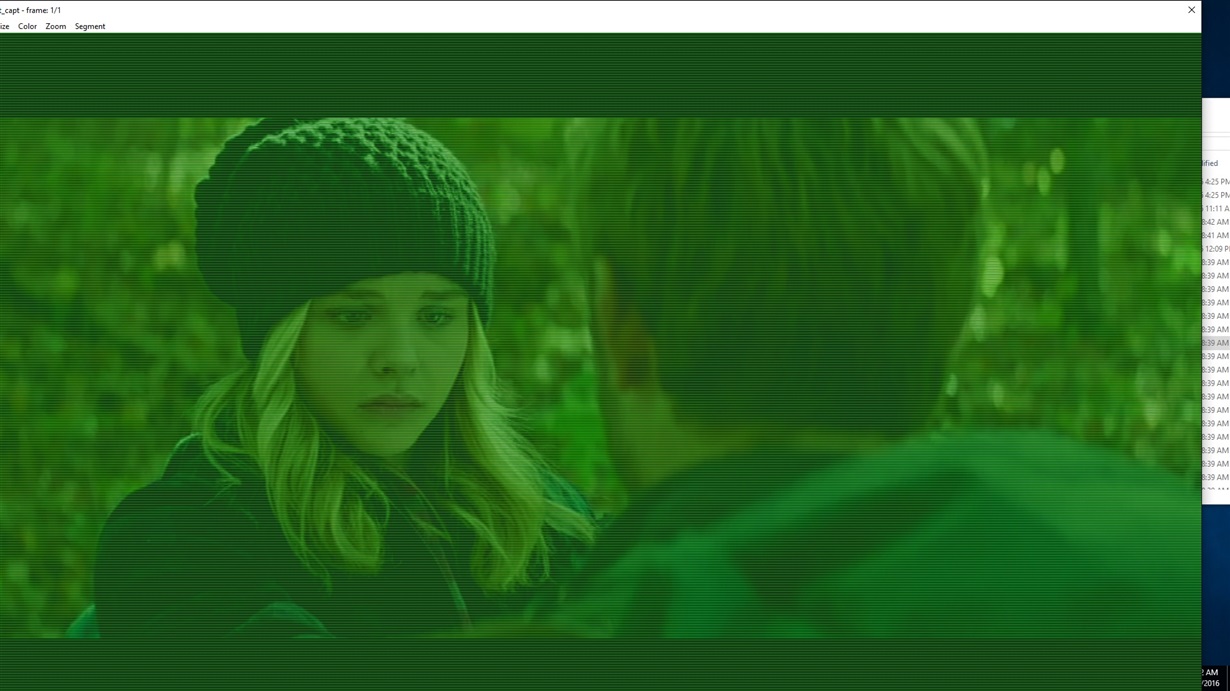

Result: Merged frame is incorrect in the way that it appears Top field from the second frame is used to merge with rest of the bottom fields always instead of merging top field and bottom field corresponding to each frame. And because of this I think the first frame captured is Correctly merged, however the rest of the frames are merged with the first frame.

Please find the attached pictures of first 3 merged frames from V4l2 Capture. Can you please provide us some details why this problem could appear and suggestions on how to resolve this? If needed please let us know any specific logs you need.

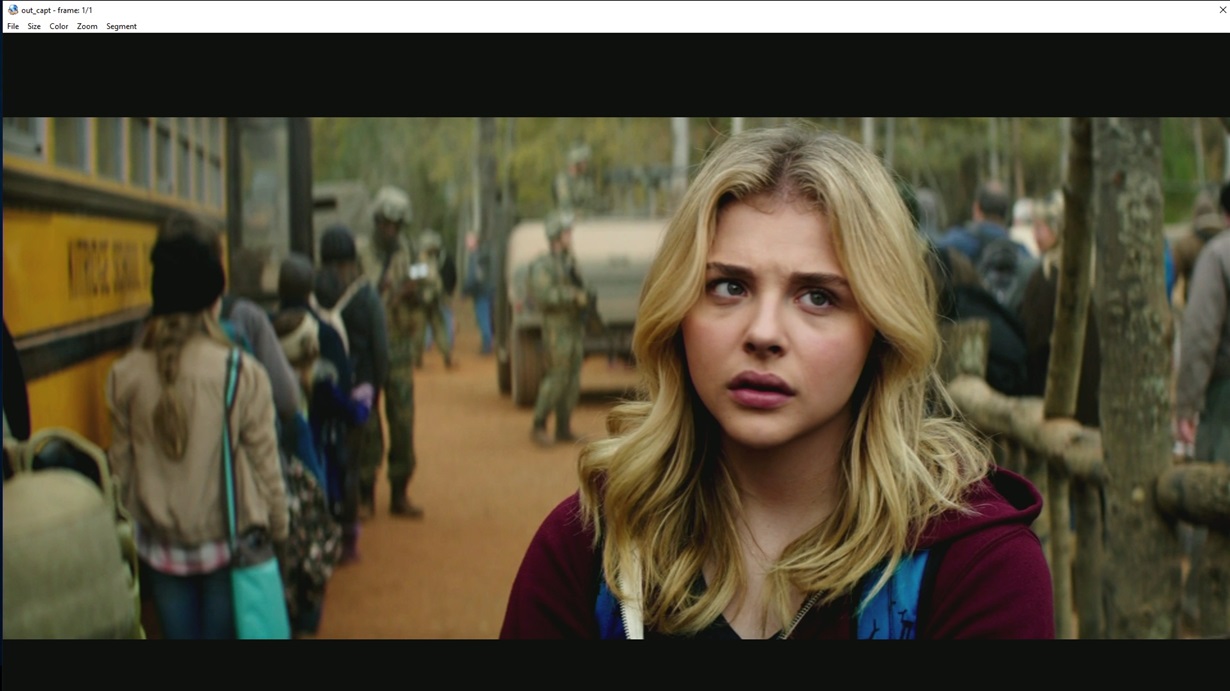

1st: Merged Correctly

2nd: Incorrectly Merged

3rd: Incorrectly merged