Hi,

It is the question about specifications of DDR2 connecting with AM3874.

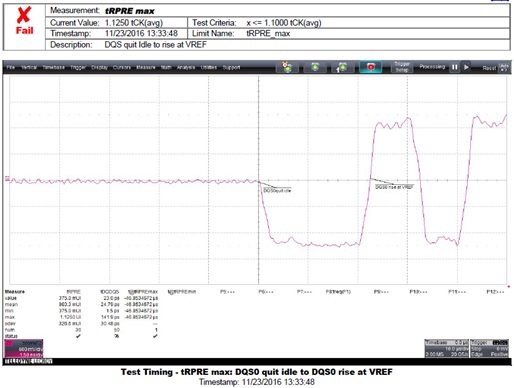

tRPRE and tRPST are defined in a timing of DQS in READ of the DDR(AM3874 catches it a side) .

When width of this tRPRE and tRPST do not slightly satisfy the specification, what kind of problem occurs in AM3874?

Best Regards,

Shigeiro Tsuda