Hi,

Table 4.5 GPIO Terminal Functions of 8168 datasheet states that the state for GPMC_A[27]/GP1[9] as below:

PULL: DIS / IPD

DRIVE: Z / Z

DVDD_3P3

PULL: A / B, where:

A is the state of the internal pull resistor during POR reset

B is the state of the internal pull resistor after POR and Warm reset are de-asserted and during Warm reset

IPD = Internal Pulldown Enabled, IPU = Internal Pullup Enabled, DIS = Internal Pull Disabled

DRIVE: A / B, where;

A is the driving state of the pin during POR reset

B is the driving state of the pin after POR and Warm reset are de-asserted and during Warm reset

H = Driving High, L = Driving Low, Z = 3-State

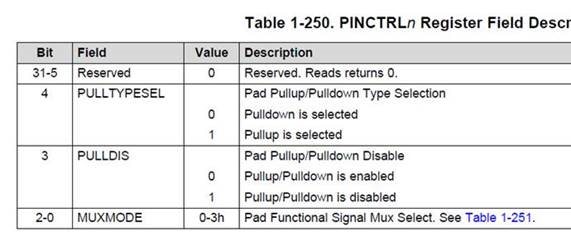

Also the technical reference manual ( ) shows that the register values for PINCTRL189 are set to

) shows that the register values for PINCTRL189 are set to

PULLTYPESEL = 0 (Pulldown selected)

PULLDIS = 0 (Pullup or Pulldown enabled)

Is there a way to hold the internal pull down resistor during the POR?

Thanks.