Hello all,

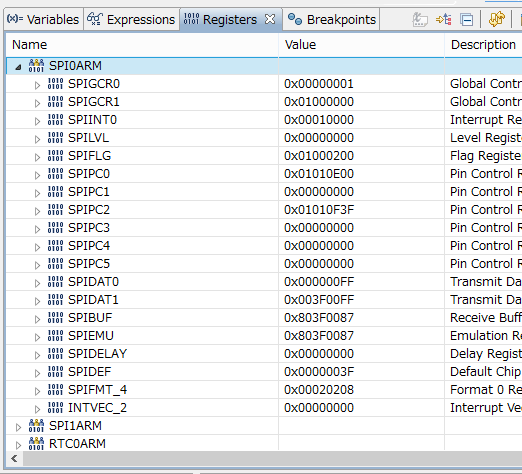

I am using OMAP-L138 and it is a SPI slave with EDMA3 to exchange packets with an external SPI master.

It works fine but it sometimes fails to exchange packets.

My problem is that EDMA3 sometimes does not complete leaving last single byte trasnfer not completed.

It seems that SPI in L138 is missing 1 or 2 SPI clocks in transfer and that it does not reach to completion of EDMA.

In fact, after sending an extra 1 or 2 SPI clocks from the external SPI master, which is a Stellaris, by manipulating GPIO registers directly to transtion rising/falling SPI clocks, then EDMA3 in the OMAP-L138 completes. And in addition the received data in OMAP are like this:

received data : 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F 20 21 22 23 24 25 26 27 28 A4 A8 AC B0 B4 B8 BC C0 C4 C8 CC D0 D4 D8 DC E0 E4 E8

expected data: 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F 20 21 22 23 24 25 26 27 28 29 2A 2B 2C 2D 2E 2F 30 31 32 33 34 35 36 37 38 39 3A 3B

Waveform in osciloscope looks fine. I do not think that this problem is from hardware/waveform issue.

Does anyone give me a suggestion?

Transfer rate is currently from 6 ~ 10MHz.

At 6.66MHz, it nevers fails.

At 8.00MHz, it sometimes fails.

At 10.00MHz, it frequently fails.

I am planing to boost it up to 20MHz of SPI transfer rate. Is this possible?

Thanks,