Hello

I have some problem with running McaSP module in Burst Mode. I need this module to send dat in to dac Converter.

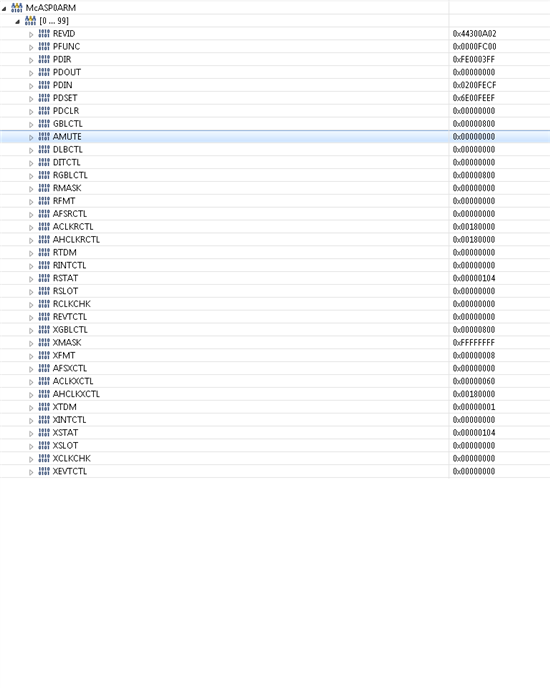

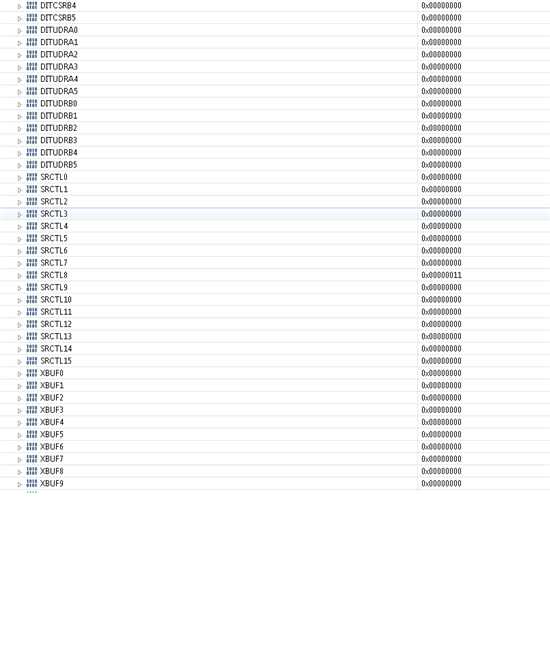

After init procedure when I try send data writes bytes in to XBUF register using AXR8 pins every 2 seconds. After that I can't see anything on output.

Here is my init Procedure:

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XMASK) = 0xFF;

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XFMT) =(1<<15);//msb first

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XFMT) |=(0xf<<4); //slot size 32 bits

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XFMT) =(1<<3); //ignore dma

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_AFSXCTL) =0; //turn off sync control register

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_ACLKXCTL) =(1<<5); //internal clock

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_ACLKXCTL) |=32; //clock divider on 32

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_ACLKXCTL) |=(1<<7);

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_AHCLKXCTL) =(1<<15); //internal closk

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_AHCLKXCTL) |=100;//divider

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XTDM) = 1; //one slot active

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XINTCTL) = 0; //turn off interrupt

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XCLKCHK) = 6; //divide 64

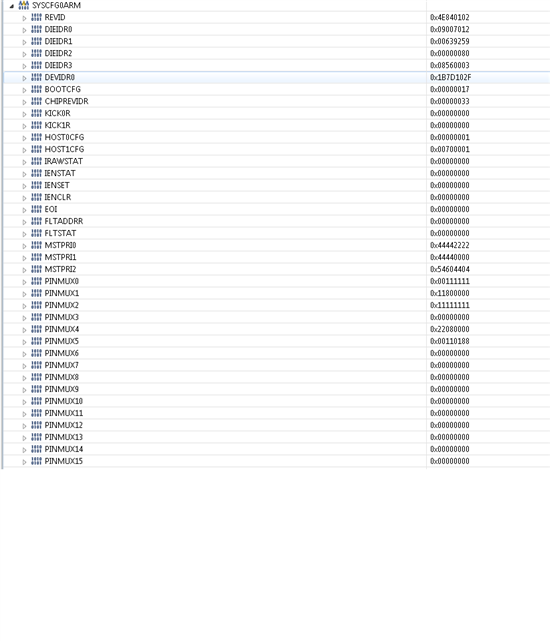

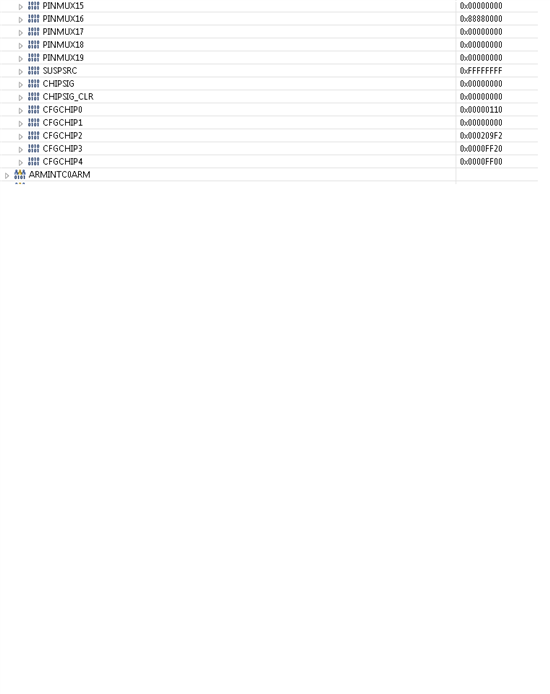

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_PFUNC) = 0xFC00; //usawienie pinow dunkcjonalnych dal modulu AXR, i pozostalych

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_PDIR) = 0xFE0003FF; //istawienie kierunku pracy dla pinow...

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_SRCTL(8)) = 1; //ustawienie serializatorow jako transmisja

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_GBLCTL) = (1<<9);

while(((SOC_MCASP_0_CTRL_REGS + MCASP_GBLCTL) & (1<<9)))

;

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_GBLCTL) = (1<<8);

while(((SOC_MCASP_0_CTRL_REGS + MCASP_GBLCTL) & (1<<8)))

;

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XSTAT) = 0x0000FFFF; //wyczyszczenie rejestru zwiazanego z statusem od nadajnika

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_GBLCTL) = (1<<10);

while(((SOC_MCASP_0_CTRL_REGS + MCASP_GBLCTL) & (1<<10)))

;

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_XBUF(8)) =0x55555555;

HWREG(SOC_MCASP_0_CTRL_REGS + MCASP_GBLCTL) = (1<<11);

while(((SOC_MCASP_0_CTRL_REGS + MCASP_GBLCTL) & (1<<11)))

;

Please help me to find where is the problems

Marek