Hi,

Our customer is using DDR2 with AM1808,

and few of the custom boards has issue(system crash) related to DDR2.

They see the data on the DDR changing constantly even when

the CPU and clocks are OFF. But restores with a reset on DDR PHY.

The DDR is configured in point-to-point, without any external termination.

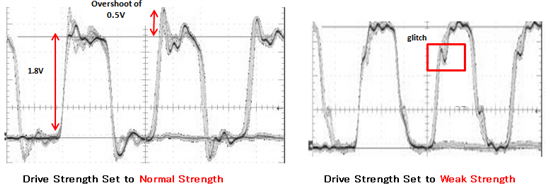

The system crashes if they use weak drive strength,

but if they use the normal drive strength, the system works normally

with significant overshoot/undershoot.

We are trying to get the customer's schematics to check if it as per the

datasheet guidelines.

Meanwhile if possible could you please comment on the below behaviour.

1.As mentioned above the DDR contents are restored to normal with a

reset on DDR PHY, what could be the reason for DDR contents restored to normal

with a reset on DDR PHY.

2.When they change the Read latency(RL) value on the DDR PHY Control Register 1 (DRPYC1R),

few working boards also started showing this crash behaviour, does it mean the

timings of the DDR memory and the board is not tuned correctly?

3.It was written on the E2E that VTP calibration is done in the ROM Bootloader

hence they don't execute the VTP calibration in their program(bootloader).

Is it necessary to do the VTP calibration in user program(like u-boot) and what could

be the effect of disabling VTP?

note: they tried to add VTP calibration code but still the issue exists.

4.They have found that touching a Probe(1pF) on DQS1 pin causes a system crash.

Does it indicates a wrong soldering or wrong via?

Regards

Prad