Symptom: Ethernet 10 Base T operation fails to receive data approximately ~ 1 out of 10 transmissions. 100 Base Tx receives no data at all. Same operation in both half and full duplex regardless of auto negotiated or forced.

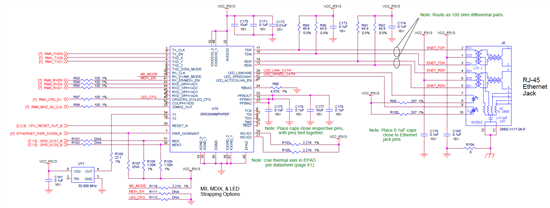

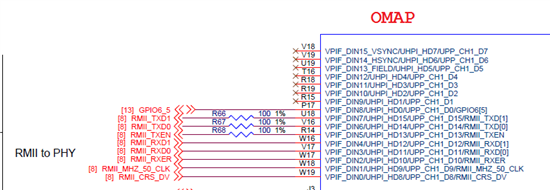

Board config: OMAP L138B-EP connected to a DP83848-EP PHY using RMII. Davinci-EMAC controlled using UBOOT and/or Linux 3.3 kernel with davinci-emac configuration leveraged from OMAP-L138 LCDK MCSDK software package but modified for use with this particular PHY and RMII. Identical symptoms with both UBOOT and Linux. The majority of testing is being performed with UBOOT.

Variables eliminated:

1) Signal integrity. The symptom would seem to point directly to this, so about the first week of debug as focused on signal integrity. Ethernet-level signal integrity has been verified with scope captures, adjustment of termination resistor location, an addition of bypass capacitors with varying levels of capacitance, and using a different set of known-good magnetics. Symptom persists with same character for both external and internal PHY loopbacks (that utilize the OMAP’s EMAC).

2) PHY configuration. PHY hardware configuration verified with correct netlist and board layout to OMAP (schematic excerpt included), rbias resistor and voltage correct, PFBOUT connections (to PFBIN 1 & 2) and capacitors correct, and strapping mode verified through register inspection. All PHY-only built-in-self-tests always pass, both internal and external loopback. PHY harmonic distortion testing passes, shows good quality. 50MHz PHY clock is oscillator generated and input into the PHY with excellent quality. The RMII_50MHz clock into the OMAP has excellent quality.

3) OMAP system configuration. Pinmuxes are set correctly, and system level clocks and PLL registers are set correctly and legally (multiple ranges of speeds were tried). No known issues with RAM or Flash operations.

4) EMAC configuration. EMAC configuration verified by comparison with working network operation on the OMAP L138 LCDK dev kit, but with modifications only for RMII operation and configuration for the DP83848 PHY. Networking logic and procedures are verified to be correct according to the L138 and DP83848 datasheets, as well as known working with the dev kit. Due to the fact that the LCDK dev kit uses MII, and works just fine for 10 and 100 base T, heavy scrutiny was given to our RMII configuration to ensure we were configuring it correctly. Speed/Duplex/Autonegotiation configuration is verified in both the PHY and EMAC through register inspection, debug statements, and hardware scoping.

Where we are:

The attached UBOOT terminal output with debug statements shows dumps from both the EMAC statistics registers and select PHY registers during a successful communication sequence and a subsequent failed communication sequence.

The communication sequence operates as follows:

1) A ping UBOOT command is issued

2) EMAC device is opened, which initializes the EMAC and sets up the descriptor pointers. A statistics register block dump is performed to show clean all zeros.

3) ARP request begins and a broadcast data packet is sent out.

4) Laptop responds with ARP reply and is received. During a receive, the EMAC statistics registers and PHY registers are dumped.

5) An ICMP echo request packet is sent out.

6) An ICMP echo reply is received and the statistics and PHY registers are again dumped.

Flash: 32 MiB

MMC: davinci: 0

In: serial

Out: serial

Err: serial

Net: PHY_DP83848 phy num: 0

Eth init done - ready for autonegotiation

num_phy: 1

Eth init done - in conditional

Entered DP83848 is phy connected - phy_addr: 1.

Between 1 and 2 - id1: 2000.

--> id1 : 0x2000--> DP83848_PHYID1_OUI : 0x2000--> id2 : 0x5c90--> DP83848_PHYID2_OUI : 0x5c90Eth init done - begin autonegotiation [0]

Entering dp83848_auto_negotiate.

dp83848_auto_negotiate - past control reg read.

-->Starting Autonegotiation!

-->Autonegotiation PASSED!

&emac->MACCONTROL register before: 0000

Set EMAC to Duplex Half Enabled!

Set EMAC to Speed 10!

&emac->MACCONTROL register after: 0000

dp83848_get_link_speed exiting...

Autoneg return: 1&emac->MACCONTROL register before: 0000

Set EMAC to Duplex Half Enabled!

Set EMAC to Speed 10!

&emac->MACCONTROL register after: 0000

dp83848_get_link_speed exiting...

Init return: 1Eth init done - autonegotiation should be done

DaVinci-EMAC

Pinmux[0] @ 0x01c14120: 0x44080000

Pinmux[1] @ 0x01c14124: 0x00000000

Pinmux[2] @ 0x01c14128: 0x88888880

Pinmux[3] @ 0x01c1412c: 0x88888888

Pinmux[4] @ 0x01c14130: 0x00222288

Pinmux[5] @ 0x01c14134: 0x11000000

Pinmux[6] @ 0x01c14138: 0x00000000

Pinmux[7] @ 0x01c1413c: 0x00110001

Pinmux[8] @ 0x01c14140: 0x11111111

Pinmux[9] @ 0x01c14144: 0x11111111

Pinmux[10] @ 0x01c14148: 0x11222222

Pinmux[11] @ 0x01c1414c: 0x11111111

Pinmux[12] @ 0x01c14150: 0x11111111

Pinmux[13] @ 0x01c14154: 0x00000000

Pinmux[14] @ 0x01c14158: 0x88888800

Pinmux[15] @ 0x01c1415c: 0x00000080

Pinmux[16] @ 0x01c14160: 0x00000000

PllRegs[0] @ 0x01c11110: 0x00000018

PllRegs[1] @ 0x01c11114: 0x00008000

PllRegs[2] @ 0x01c11118: 0x00008000

PllRegs[3] @ 0x01c1111c: 0x00008001

PllRegs[4] @ 0x01c11120: 0x00008004

PllRegs[5] @ 0x01c11124: 0x00008000

PllRegs[6] @ 0x01c11128: 0x00008001

PllRegs[7] @ 0x01c1112c: 0x00000000

PllRegs[8] @ 0x01c11130: 0x00000000

PllRegs[9] @ 0x01c11134: 0x00000000

PllRegs[10] @ 0x01c11138: 0x00000001

PllRegs[11] @ 0x01c1113c: 0x00000006

PllRegs[12] @ 0x01c11140: 0x000001ff

PllRegs[13] @ 0x01c11144: 0x00000000

PllRegs[14] @ 0x01c11148: 0x00000003

PllRegs[15] @ 0x01c1114c: 0x00000003

PllRegs[16] @ 0x01c11150: 0x000001ff

PllRegs[17] @ 0x01c11154: 0x00000000

PllRegs[18] @ 0x01c11158: 0x00000000

PllRegs[19] @ 0x01c1115c: 0x00000000

PllRegs[20] @ 0x01c11160: 0x00008003

PllRegs[21] @ 0x01c11164: 0x00008002

PllRegs[22] @ 0x01c11168: 0x00008000

PllRegs[23] @ 0x01c1116c: 0x00008005

PllRegs[24] @ 0x01c11170: 0x00008005

Hit any key to stop autoboot: 0

U-Boot > ping 192.168.1.95

StatRegs BaseAddr 0x00000000 0x00000004 0x00000008 0x0000000c

|------------------|-----------|----------|----------|----------|----------|

StatReg[00..04] @ 0x01e23200: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[04..08] @ 0x01e23210: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[08..12] @ 0x01e23220: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[12..16] @ 0x01e23230: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[16..20] @ 0x01e23240: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[20..24] @ 0x01e23250: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[24..28] @ 0x01e23260: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[28..32] @ 0x01e23270: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[32..36] @ 0x01e23280: 0x00000000 0x00000000 0x00000000 0x00000000

WE DID IT!

&emac->MACCONTROL register before: 8021

Set EMAC to Duplex Half Enabled!

Set EMAC to Speed 10!

&emac->MACCONTROL register after: 0020

dp83848_get_link_speed exiting...

Using DaVinci-EMAC device

============STARTING PING=============

sending ARP for 5f01a8c0

ARP broadcast 1

&emac->MACCONTROL register before: 0020

Set EMAC to Duplex Half Enabled!

Set EMAC to Speed 10!

&emac->MACCONTROL register after: 0020

dp83848_get_link_speed exiting...

Rx Header Desc Pointer: 0x01e20000

emac_rx_active_head: 0x01e20000

emac_rx_active_head->pkt_flag_len: 0xc000003c

(emac_rx_active_head+1)->pkt_flag_len: 0x20000000

(emac_rx_active_head+2)->pkt_flag_len: 0x20000000

StatRegs BaseAddr 0x00000000 0x00000004 0x00000008 0x0000000c

|------------------|-----------|----------|----------|----------|----------|

StatReg[00..04] @ 0x01e23200: 0x00000001 0x00000000 0x00000000 0x00000000

StatReg[04..08] @ 0x01e23210: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[08..12] @ 0x01e23220: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[12..16] @ 0x01e23230: 0x00000040 0x00000001 0x00000001 0x00000000

StatReg[16..20] @ 0x01e23240: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[20..24] @ 0x01e23250: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[24..28] @ 0x01e23260: 0x00000000 0x00000040 0x00000002 0x00000000

StatReg[28..32] @ 0x01e23270: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[32..36] @ 0x01e23280: 0x00000080 0x00000000 0x00000000 0x00000000

DP83848_PHY_STAT_REG (0x10): 4113

DP83848_FALSE_SNS_CNTR_REG (0x14): 0000

DP83848_RX_ERROR_CNTR_REG (0x15): 0000

DP83848_ENG_DTCT_CTRL_REG (0x1d): 6011

Got ARP

&emac->MACCONTROL register before: 0020

Set EMAC to Duplex Half Enabled!

Set EMAC to Speed 10!

&emac->MACCONTROL register after: 0020

dp83848_get_link_speed exiting...

Rx Header Desc Pointer: 0x01e20010

emac_rx_active_head: 0x01e20010

emac_rx_active_head->pkt_flag_len: 0xc000003c

(emac_rx_active_head+1)->pkt_flag_len: 0x20000000

(emac_rx_active_head+2)->pkt_flag_len: 0x20000000

StatRegs BaseAddr 0x00000000 0x00000004 0x00000008 0x0000000c

|------------------|-----------|----------|----------|----------|----------|

StatReg[00..04] @ 0x01e23200: 0x00000002 0x00000000 0x00000000 0x00000000

StatReg[04..08] @ 0x01e23210: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[08..12] @ 0x01e23220: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[12..16] @ 0x01e23230: 0x00000080 0x00000002 0x00000001 0x00000000

StatReg[16..20] @ 0x01e23240: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[20..24] @ 0x01e23250: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[24..28] @ 0x01e23260: 0x00000000 0x00000080 0x00000004 0x00000000

StatReg[28..32] @ 0x01e23270: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[32..36] @ 0x01e23280: 0x00000100 0x00000000 0x00000000 0x00000000

DP83848_PHY_STAT_REG (0x10): 4113

DP83848_FALSE_SNS_CNTR_REG (0x14): 0000

DP83848_RX_ERROR_CNTR_REG (0x15): 0000

DP83848_ENG_DTCT_CTRL_REG (0x1d): 6011

Got ICMP ECHO REPLY, return 42 bytes

host 192.168.1.95 is alive

U-Boot > ping 192.168.1.95

StatRegs BaseAddr 0x00000000 0x00000004 0x00000008 0x0000000c

|------------------|-----------|----------|----------|----------|----------|

StatReg[00..04] @ 0x01e23200: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[04..08] @ 0x01e23210: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[08..12] @ 0x01e23220: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[12..16] @ 0x01e23230: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[16..20] @ 0x01e23240: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[20..24] @ 0x01e23250: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[24..28] @ 0x01e23260: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[28..32] @ 0x01e23270: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[32..36] @ 0x01e23280: 0x00000000 0x00000000 0x00000000 0x00000000

WE DID IT!

&emac->MACCONTROL register before: 8021

Set EMAC to Duplex Half Enabled!

Set EMAC to Speed 10!

&emac->MACCONTROL register after: 0020

dp83848_get_link_speed exiting...

Using DaVinci-EMAC device

============STARTING PING=============

sending ARP for 5f01a8c0

ARP broadcast 1

&emac->MACCONTROL register before: 0020

Set EMAC to Duplex Half Enabled!

Set EMAC to Speed 10!

&emac->MACCONTROL register after: 0020

dp83848_get_link_speed exiting...

Rx Header Desc Pointer: 0x01e20000

emac_rx_active_head: 0x01e20000

emac_rx_active_head->pkt_flag_len: 0x20000000

(emac_rx_active_head+1)->pkt_flag_len: 0x20000000

(emac_rx_active_head+2)->pkt_flag_len: 0x20000000

StatRegs BaseAddr 0x00000000 0x00000004 0x00000008 0x0000000c

|------------------|-----------|----------|----------|----------|----------|

StatReg[00..04] @ 0x01e23200: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[04..08] @ 0x01e23210: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[08..12] @ 0x01e23220: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[12..16] @ 0x01e23230: 0x00000000 0x00000001 0x00000001 0x00000000

StatReg[16..20] @ 0x01e23240: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[20..24] @ 0x01e23250: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[24..28] @ 0x01e23260: 0x00000000 0x00000040 0x00000001 0x00000000

StatReg[28..32] @ 0x01e23270: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[32..36] @ 0x01e23280: 0x00000081 0x00000000 0x00000000 0x00000000

DP83848_PHY_STAT_REG (0x10): 4113

DP83848_FALSE_SNS_CNTR_REG (0x14): 0000

DP83848_RX_ERROR_CNTR_REG (0x15): 0000

DP83848_ENG_DTCT_CTRL_REG (0x1d): 6011

Rx Header Desc Pointer: 0x01e20000

emac_rx_active_head: 0x01e20000

emac_rx_active_head->pkt_flag_len: 0x20000000

(emac_rx_active_head+1)->pkt_flag_len: 0x20000000

(emac_rx_active_head+2)->pkt_flag_len: 0x20000000

StatRegs BaseAddr 0x00000000 0x00000004 0x00000008 0x0000000c

|------------------|-----------|----------|----------|----------|----------|

StatReg[00..04] @ 0x01e23200: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[04..08] @ 0x01e23210: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[08..12] @ 0x01e23220: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[12..16] @ 0x01e23230: 0x00000000 0x00000001 0x00000001 0x00000000

StatReg[16..20] @ 0x01e23240: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[20..24] @ 0x01e23250: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[24..28] @ 0x01e23260: 0x00000000 0x00000040 0x00000001 0x00000000

StatReg[28..32] @ 0x01e23270: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[32..36] @ 0x01e23280: 0x00000081 0x00000000 0x00000000 0x00000000

DP83848_PHY_STAT_REG (0x10): 4113

DP83848_FALSE_SNS_CNTR_REG (0x14): 0000

DP83848_RX_ERROR_CNTR_REG (0x15): 0000

DP83848_ENG_DTCT_CTRL_REG (0x1d): 6011

ARP broadcast 2

&emac->MACCONTROL register before: 0020

Set EMAC to Duplex Half Enabled!

Set EMAC to Speed 10!

&emac->MACCONTROL register after: 0020

dp83848_get_link_speed exiting...

Rx Header Desc Pointer: 0x01e20000

emac_rx_active_head: 0x01e20000

emac_rx_active_head->pkt_flag_len: 0x20000000

(emac_rx_active_head+1)->pkt_flag_len: 0x20000000

(emac_rx_active_head+2)->pkt_flag_len: 0x20000000

StatRegs BaseAddr 0x00000000 0x00000004 0x00000008 0x0000000c

|------------------|-----------|----------|----------|----------|----------|

StatReg[00..04] @ 0x01e23200: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[04..08] @ 0x01e23210: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[08..12] @ 0x01e23220: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[12..16] @ 0x01e23230: 0x00000000 0x00000002 0x00000002 0x00000000

StatReg[16..20] @ 0x01e23240: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[20..24] @ 0x01e23250: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[24..28] @ 0x01e23260: 0x00000000 0x00000080 0x00000002 0x00000000

StatReg[28..32] @ 0x01e23270: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[32..36] @ 0x01e23280: 0x00000102 0x00000000 0x00000000 0x00000000

DP83848_PHY_STAT_REG (0x10): 4113

DP83848_FALSE_SNS_CNTR_REG (0x14): 0000

DP83848_RX_ERROR_CNTR_REG (0x15): 0000

DP83848_ENG_DTCT_CTRL_REG (0x1d): 6011

Rx Header Desc Pointer: 0x01e20000

emac_rx_active_head: 0x01e20000

emac_rx_active_head->pkt_flag_len: 0x20000000

(emac_rx_active_head+1)->pkt_flag_len: 0x20000000

(emac_rx_active_head+2)->pkt_flag_len: 0x20000000

StatRegs BaseAddr 0x00000000 0x00000004 0x00000008 0x0000000c

|------------------|-----------|----------|----------|----------|----------|

StatReg[00..04] @ 0x01e23200: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[04..08] @ 0x01e23210: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[08..12] @ 0x01e23220: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[12..16] @ 0x01e23230: 0x00000000 0x00000002 0x00000002 0x00000000

StatReg[16..20] @ 0x01e23240: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[20..24] @ 0x01e23250: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[24..28] @ 0x01e23260: 0x00000000 0x00000080 0x00000002 0x00000000

StatReg[28..32] @ 0x01e23270: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[32..36] @ 0x01e23280: 0x00000102 0x00000000 0x00000000 0x00000000

DP83848_PHY_STAT_REG (0x10): 4113

DP83848_FALSE_SNS_CNTR_REG (0x14): 0000

DP83848_RX_ERROR_CNTR_REG (0x15): 0000

DP83848_ENG_DTCT_CTRL_REG (0x1d): 6011

ARP broadcast 3

&emac->MACCONTROL register before: 0020

Set EMAC to Duplex Half Enabled!

Set EMAC to Speed 10!

&emac->MACCONTROL register after: 0020

dp83848_get_link_speed exiting...

Rx Header Desc Pointer: 0x01e20000

emac_rx_active_head: 0x01e20000

emac_rx_active_head->pkt_flag_len: 0x20000000

(emac_rx_active_head+1)->pkt_flag_len: 0x20000000

(emac_rx_active_head+2)->pkt_flag_len: 0x20000000

StatRegs BaseAddr 0x00000000 0x00000004 0x00000008 0x0000000c

|------------------|-----------|----------|----------|----------|----------|

StatReg[00..04] @ 0x01e23200: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[04..08] @ 0x01e23210: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[08..12] @ 0x01e23220: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[12..16] @ 0x01e23230: 0x00000000 0x00000003 0x00000003 0x00000000

StatReg[16..20] @ 0x01e23240: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[20..24] @ 0x01e23250: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[24..28] @ 0x01e23260: 0x00000000 0x000000c0 0x00000003 0x00000000

StatReg[28..32] @ 0x01e23270: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[32..36] @ 0x01e23280: 0x00000182 0x00000000 0x00000000 0x00000000

DP83848_PHY_STAT_REG (0x10): 4113

DP83848_FALSE_SNS_CNTR_REG (0x14): 0000

DP83848_RX_ERROR_CNTR_REG (0x15): 0000

DP83848_ENG_DTCT_CTRL_REG (0x1d): 6011

Rx Header Desc Pointer: 0x01e20000

emac_rx_active_head: 0x01e20000

emac_rx_active_head->pkt_flag_len: 0x20000000

(emac_rx_active_head+1)->pkt_flag_len: 0x20000000

(emac_rx_active_head+2)->pkt_flag_len: 0x20000000

StatRegs BaseAddr 0x00000000 0x00000004 0x00000008 0x0000000c

|------------------|-----------|----------|----------|----------|----------|

StatReg[00..04] @ 0x01e23200: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[04..08] @ 0x01e23210: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[08..12] @ 0x01e23220: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[12..16] @ 0x01e23230: 0x00000000 0x00000003 0x00000003 0x00000000

StatReg[16..20] @ 0x01e23240: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[20..24] @ 0x01e23250: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[24..28] @ 0x01e23260: 0x00000000 0x000000c0 0x00000003 0x00000000

StatReg[28..32] @ 0x01e23270: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[32..36] @ 0x01e23280: 0x00000182 0x00000000 0x00000000 0x00000000

DP83848_PHY_STAT_REG (0x10): 4113

DP83848_FALSE_SNS_CNTR_REG (0x14): 0000

DP83848_RX_ERROR_CNTR_REG (0x15): 0000

DP83848_ENG_DTCT_CTRL_REG (0x1d): 6011

ARP broadcast 4

&emac->MACCONTROL register before: 0020

Set EMAC to Duplex Half Enabled!

Set EMAC to Speed 10!

&emac->MACCONTROL register after: 0020

dp83848_get_link_speed exiting...

Rx Header Desc Pointer: 0x01e20000

emac_rx_active_head: 0x01e20000

emac_rx_active_head->pkt_flag_len: 0x20000000

(emac_rx_active_head+1)->pkt_flag_len: 0x20000000

(emac_rx_active_head+2)->pkt_flag_len: 0x20000000

StatRegs BaseAddr 0x00000000 0x00000004 0x00000008 0x0000000c

|------------------|-----------|----------|----------|----------|----------|

StatReg[00..04] @ 0x01e23200: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[04..08] @ 0x01e23210: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[08..12] @ 0x01e23220: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[12..16] @ 0x01e23230: 0x00000000 0x00000004 0x00000004 0x00000000

StatReg[16..20] @ 0x01e23240: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[20..24] @ 0x01e23250: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[24..28] @ 0x01e23260: 0x00000000 0x00000100 0x00000004 0x00000000

StatReg[28..32] @ 0x01e23270: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[32..36] @ 0x01e23280: 0x00000202 0x00000000 0x00000000 0x00000000

DP83848_PHY_STAT_REG (0x10): 4113

DP83848_FALSE_SNS_CNTR_REG (0x14): 0000

DP83848_RX_ERROR_CNTR_REG (0x15): 0000

DP83848_ENG_DTCT_CTRL_REG (0x1d): 6011

Rx Header Desc Pointer: 0x01e20000

emac_rx_active_head: 0x01e20000

emac_rx_active_head->pkt_flag_len: 0x20000000

(emac_rx_active_head+1)->pkt_flag_len: 0x20000000

(emac_rx_active_head+2)->pkt_flag_len: 0x20000000

StatRegs BaseAddr 0x00000000 0x00000004 0x00000008 0x0000000c

|------------------|-----------|----------|----------|----------|----------|

StatReg[00..04] @ 0x01e23200: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[04..08] @ 0x01e23210: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[08..12] @ 0x01e23220: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[12..16] @ 0x01e23230: 0x00000000 0x00000004 0x00000004 0x00000000

StatReg[16..20] @ 0x01e23240: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[20..24] @ 0x01e23250: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[24..28] @ 0x01e23260: 0x00000000 0x00000100 0x00000004 0x00000000

StatReg[28..32] @ 0x01e23270: 0x00000000 0x00000000 0x00000000 0x00000000

StatReg[32..36] @ 0x01e23280: 0x00000202 0x00000000 0x00000000 0x00000000

DP83848_PHY_STAT_REG (0x10): 4113

DP83848_FALSE_SNS_CNTR_REG (0x14): 0000

DP83848_RX_ERROR_CNTR_REG (0x15): 0000

DP83848_ENG_DTCT_CTRL_REG (0x1d): 6011

Abort

ping failed; host 192.168.1.95 is not alive

U-Boot >

Items to note about a successful communication sequence: After the first ARP request transmit and ARP reply receive, tThe value of the EMAC register, RXOCTECTS (0x01e23230), shows 0x40 bytes of good data received, the value of the EMAC register, TXOCTECTS (0x01e23264), shows 0x40 bytes of good data transmitted, and the value of NETOCTETS (0x01e23280) shows a total of 0x80 bytes RX and TX data.

Items to note about a failed communication sequence: After the first ARP request transmit, there is NO RECEIVE of the ARP reply, even though we see it being sent with wireshark on the communicating laptop. The packet receive function gets stuck in a loop because the RX descriptor data never releases from its initial configuration. The value of the EMAC register, TXOCTECTS (0x01e23264), shows 0x40 bytes of good data transmitted, the value of RXOCTECTS shows ZERO bytes transmitted, but the value of NETOCTETS (0x01e23280) shows a total of 0x81 bytes RX and TX data. This implies the data was physically received by the PHY, transmitted to the EMAC over RMII, but for some reason not presented into the receive descriptor memory. A description of the NETOCTETS register implies this is due to the data being transmitted before a carrier-loss was experienced. But when we probe the CRS_DV signal on both successful and failed 10 Base T receives, we see the same one-toggle of the CRS_DV (indicating carrier sense was de-asserted). At the end of every failed (they all fail) 100 Base TX receives, we see 3 toggles of the CRS_DV signal (see scope trace). Because we see this every time, we don’t understand why sometimes RXOCTECTS is zero, and sometimes it is full.

Channel 1 (yellow) CRS_DV (at end of RMII packet)

Channel 3 (purple) RxD[0]

This implied that there might be a problem with us losing the carrier signal, and we are aware that we are not isolating the PHY’s analog power section using a ferrite bead and additional decoupling. We tried adding quite a bit of extra decoupling on our board 3x 0.22uF, 10uF and 100uF right next to the PHY’s analog section to hopefully quite it down enough, but we saw no effect on the character of the failures. It’s still not out of the question that properly isolating the quiet section would fix it, but it is very difficult for us to prove at this time without a board re-spin.

Therefore, any other thoughts on why data is not getting received?