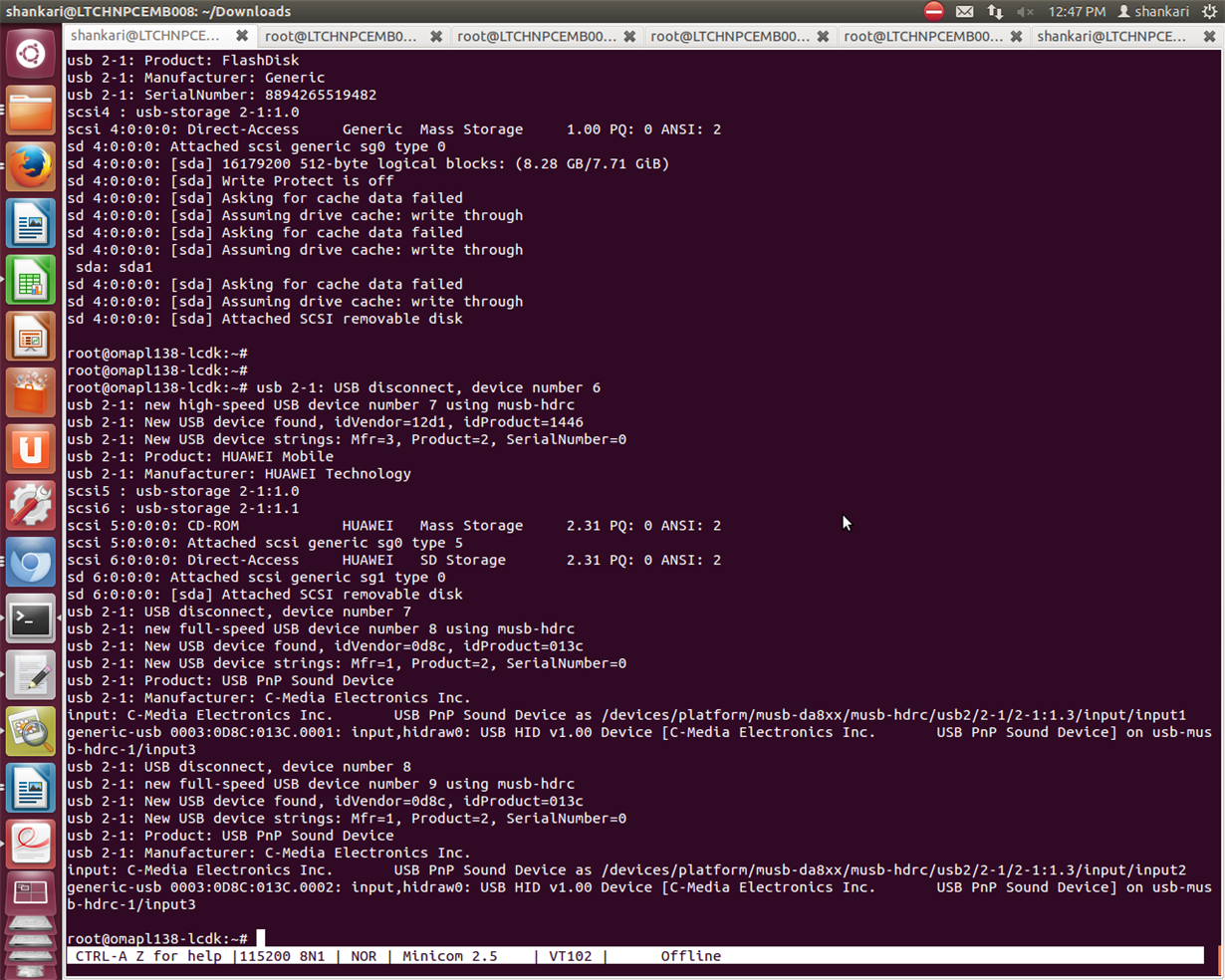

I have a custom OMAP L138 board where I am using the USB controller in an OTG configuration. This is using Linux package 3.22.0.6. Until now we have largely used the USB port in client mode to connect to a PC. Recently we have been doing more tests with our board in USB host mode to connect to various devices.

In general those devices have been working. However I've run into a problem that occurs occasionally when disconnecting the device from our board. Sometimes the USB driver appears to get latched up after disconnecting a device and no further connects (either to a PC or to a device) will occur. I've tracked the problem down to the fact that sometimes (there may be a race condition involved) the interrupt handler does not get called for the DRVVBUS interrupt, which means that the OTG state doesn't get cleaned up.

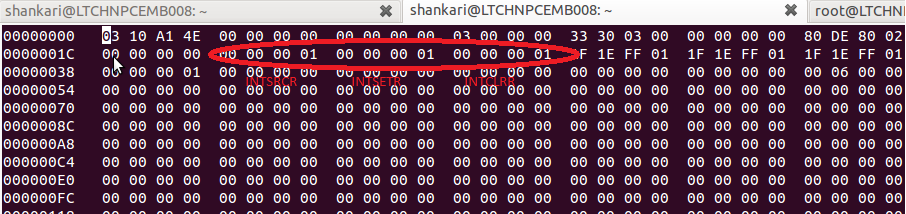

After some investigation I've found that at the point where the DRVVBUS interrupt should be occuring (after DEVCTL:SESSION is cleared), the bit is set in the INTMSKR register, but the interrupt handler never gets called. Can anyone explain why that interrupt might not be occuring? I double-checked that CTRLR:UINT is zero, but maybe there is some other configuration that is preventing the interrupt from occuring?

Any explanation or workaround would be appreciated.

Thanks,

Brian