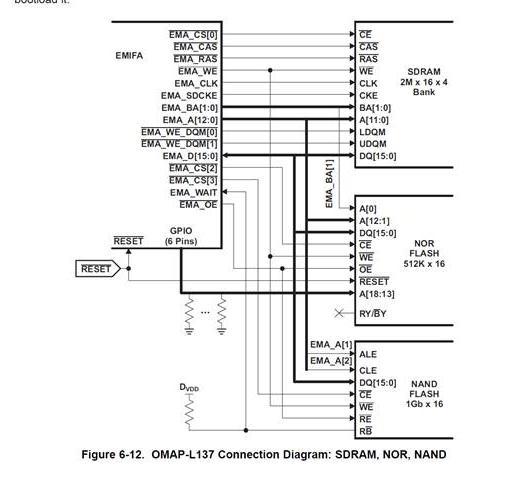

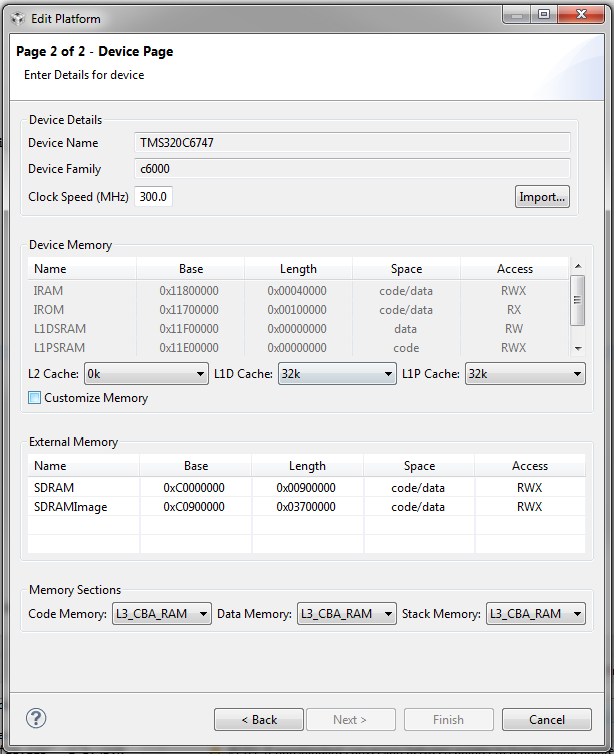

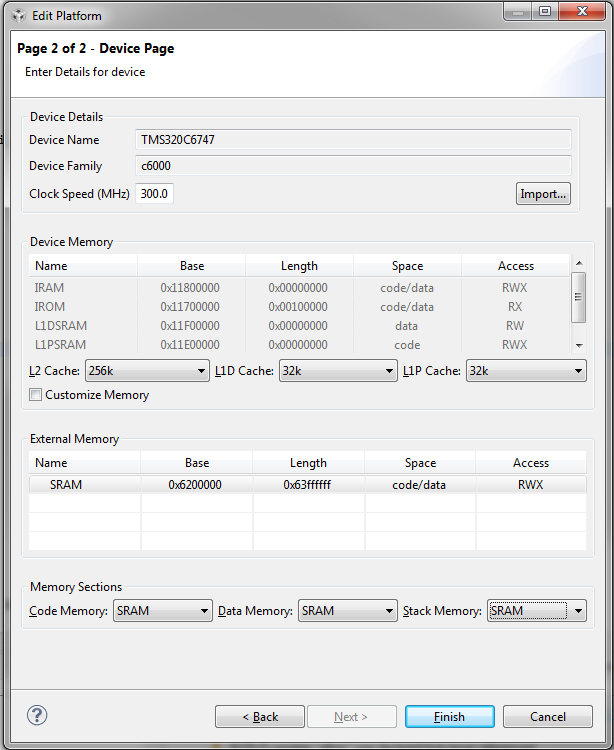

I have a project I am currently working with that I would like to boot the DSP on my OMAP L137 processor to SRAM instead of SDRAM. In the data sheet I have found the memory mapping for the asynchronous memory for the DSP, along with how to define the memory locations for program and data memory in CCS through the platform definition. The only piece of the puzzle I have is how to get the boot-loader/boot process that is defined by the AIS GEN tool to allow the boot sequence to write to the SRAM on the EMIFA bus. This doesn't seem to be an option in the AIS GEN tool so I was wondering if it is possible or if the only way to boot and run large programs for the OMAP L137 is to boot into SDRAM?

One option I thought of was to write my own bootloader, which is small enough to fit into the processors internal memory. I then allow this to configure the SRAM interface to that section of memory, and even copy the program into memory if necessary. Then jump to the program in the SRAM once the program is running. This seems complicated, and not sure if it would work given the way everything is defined. Any information or experience along these lines would be helpful.

Some information about my setup:

I am using an SPI EEProm for my non-volatile program memory and my boot mode is set to SPI.

I am using CCS Version: Version: 6.0.1.00040

Thanks,

Chris