We can see there are two CCs in OMAPL138 DSP core. I think they are physically independent of each other.

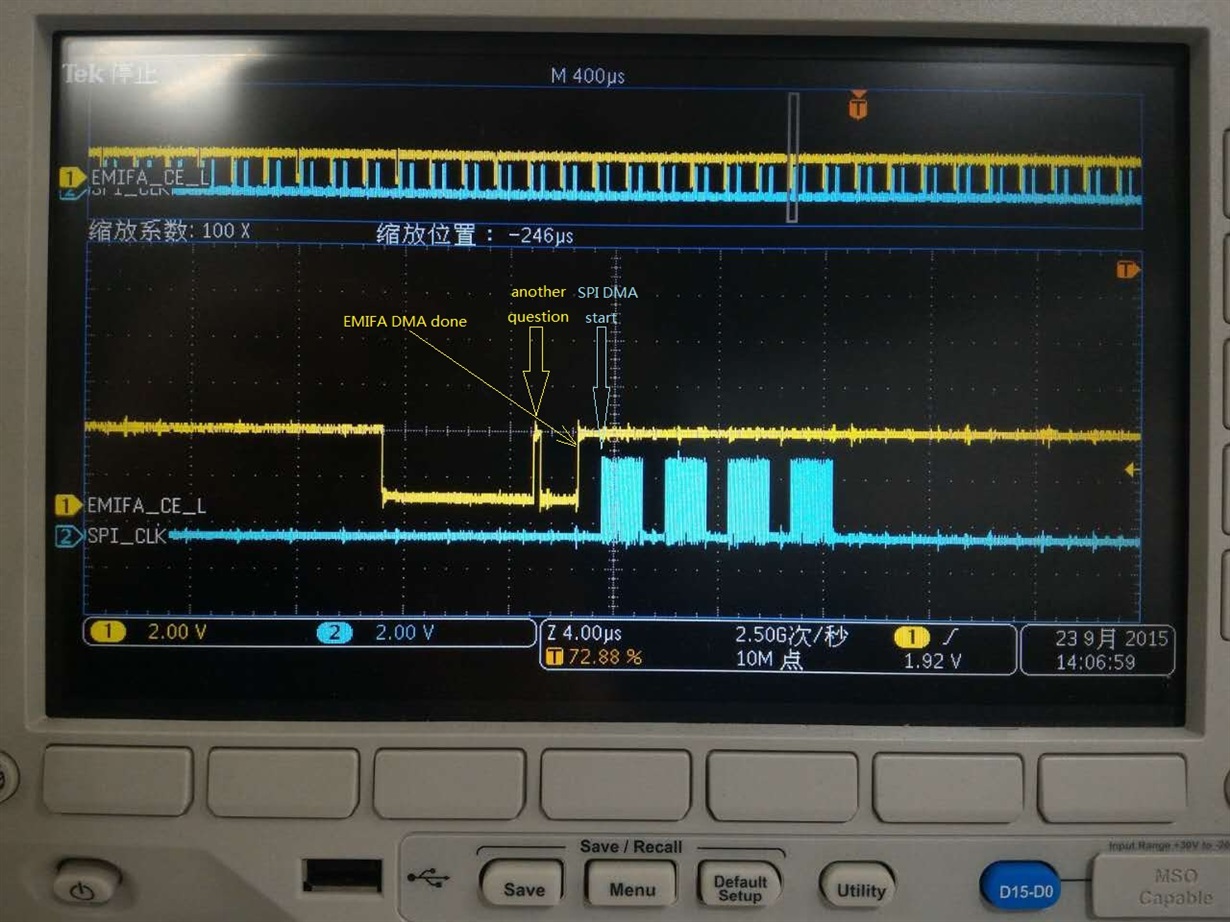

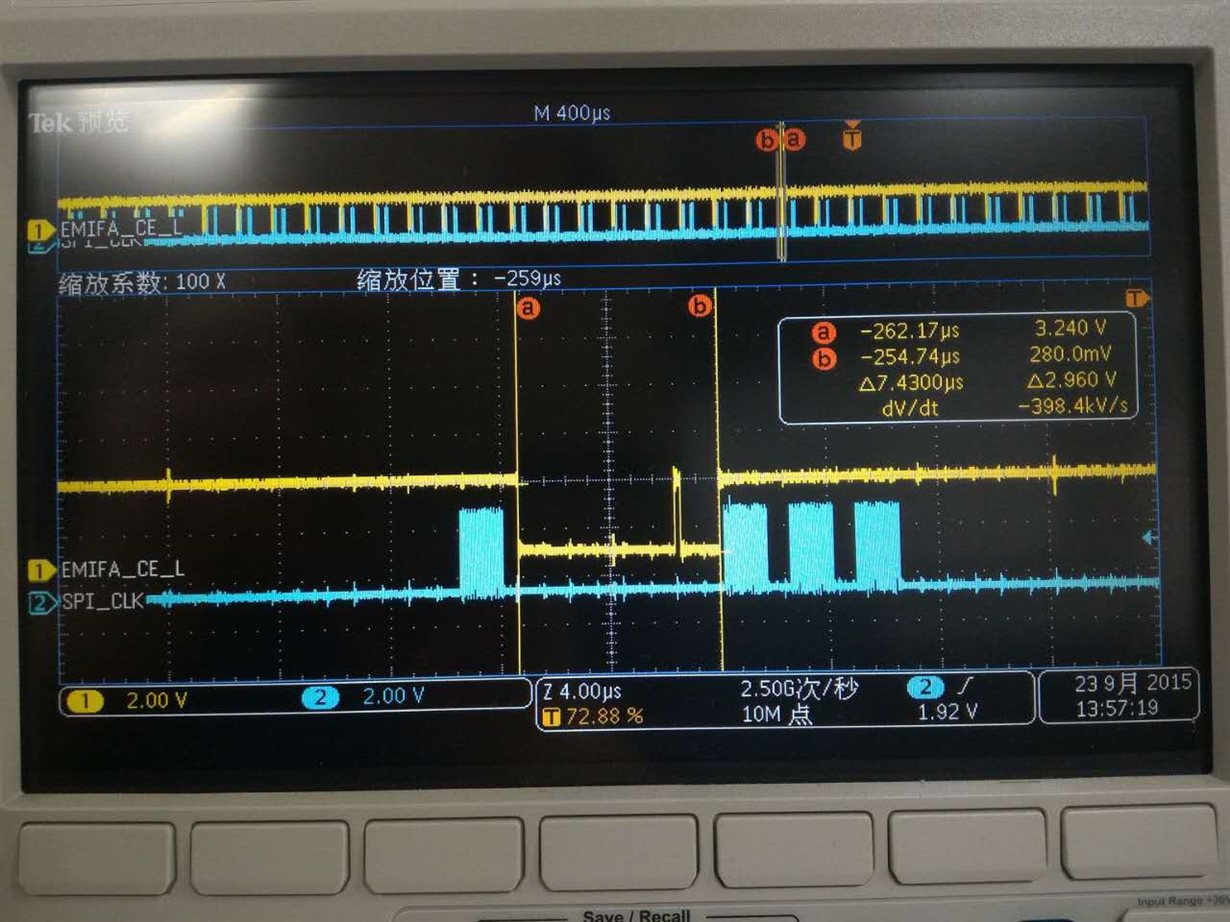

But when I trigger a A-xfer DMA belongs to 0CC0 and a B-xfer DMA belongs to 1CC0 at a same time, I found that the two DMA xfers were executed in sequence via oscilloscope.

Why is that? I want two DMAs to be executed at a same time so that time consumption could be saved. Can OMAP do that?