Hi all,

After sorting out the previous problem with the Gel script I have been going though it and writing my own based on the AM1707 script. However when I run it, there are still problems. The device becomes unresponsive very similar to before but I've checked that I'm not writing anything to reserved bits this time.

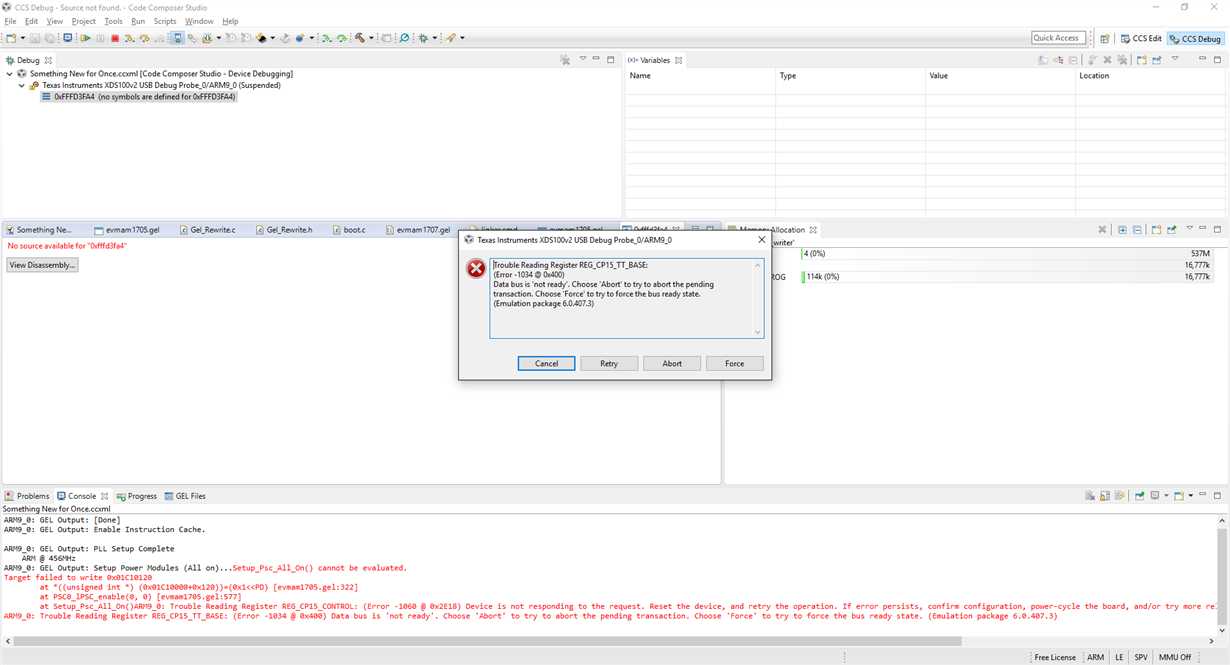

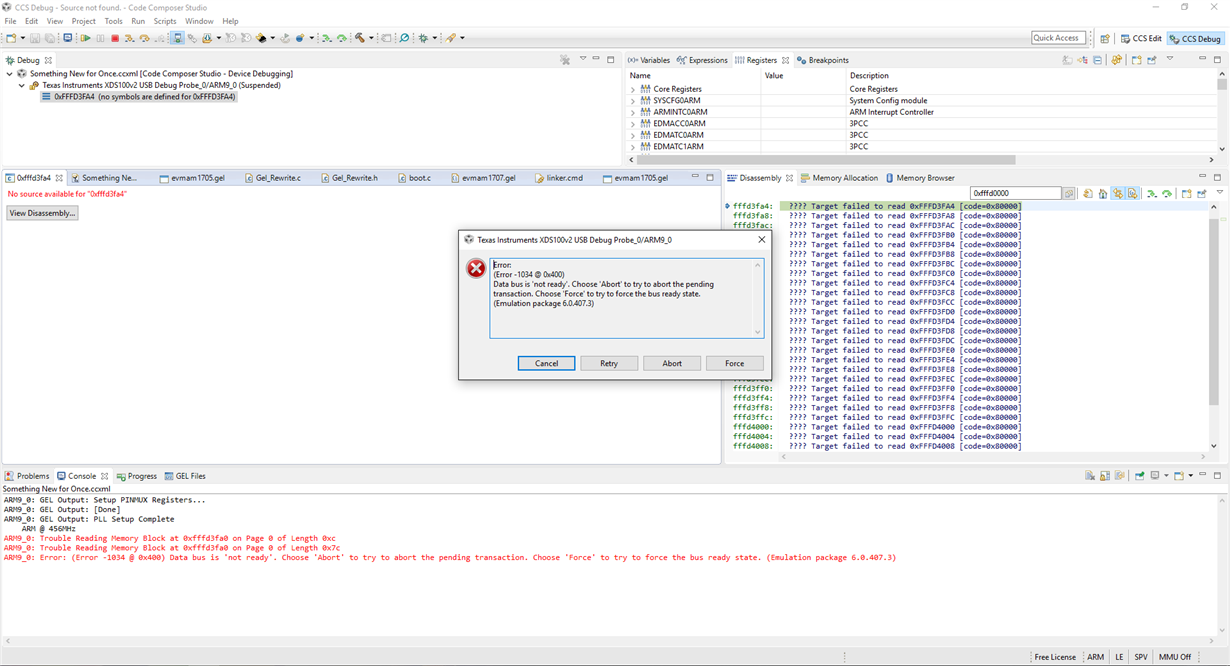

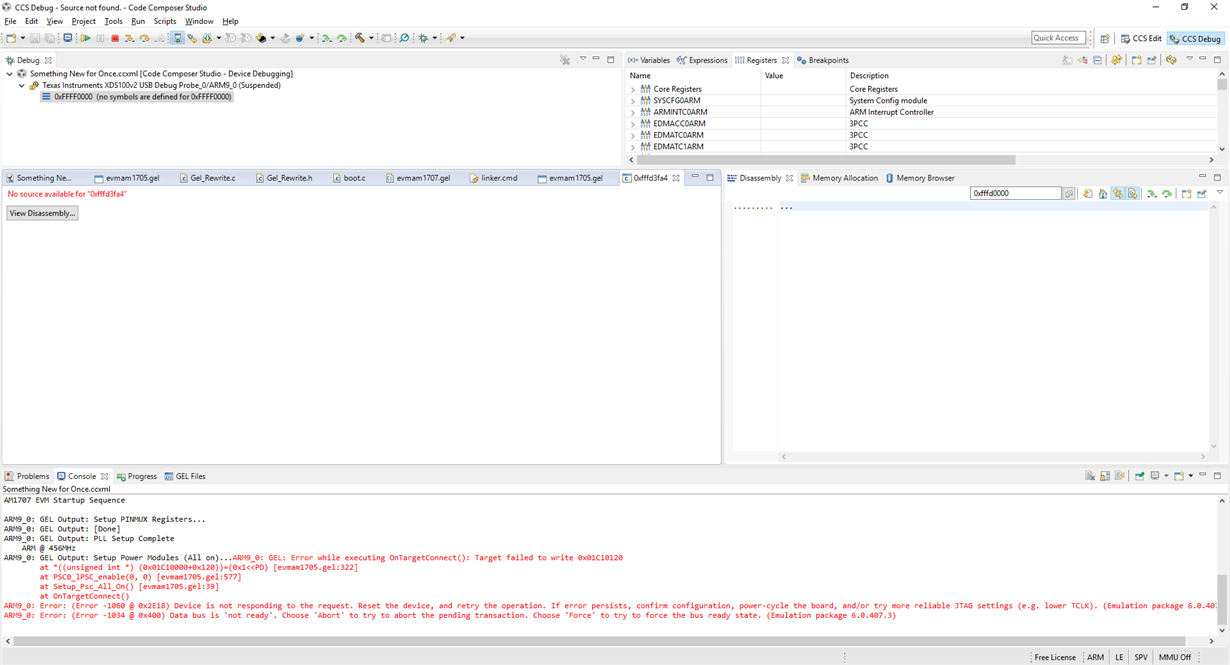

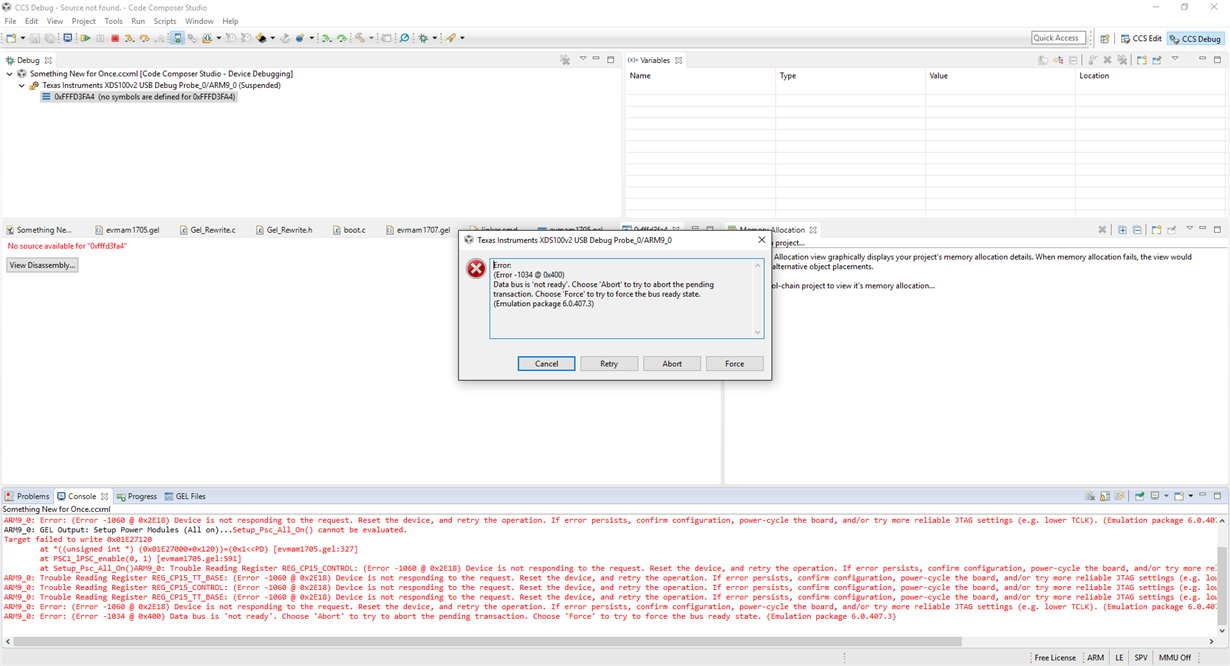

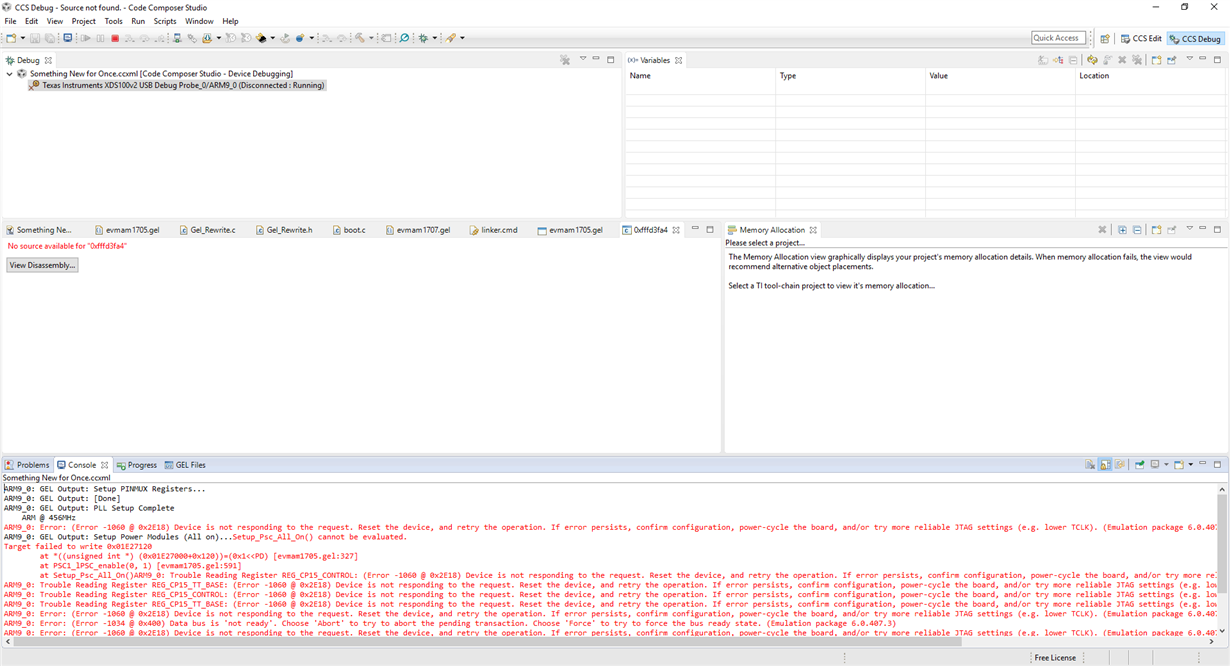

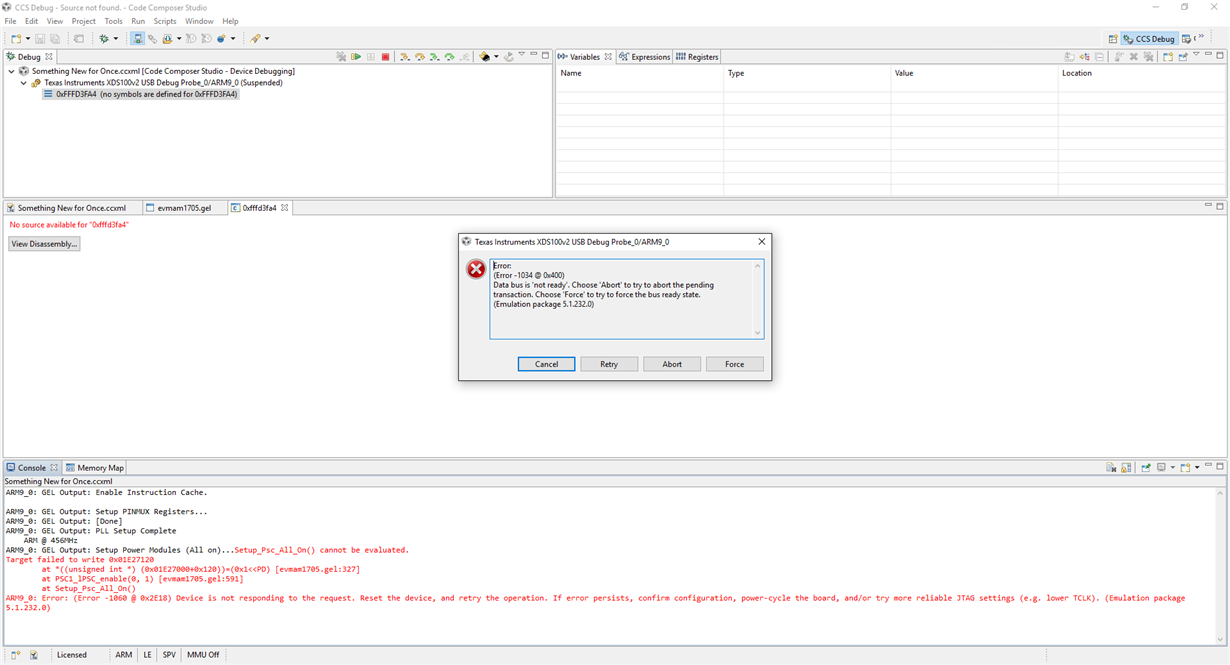

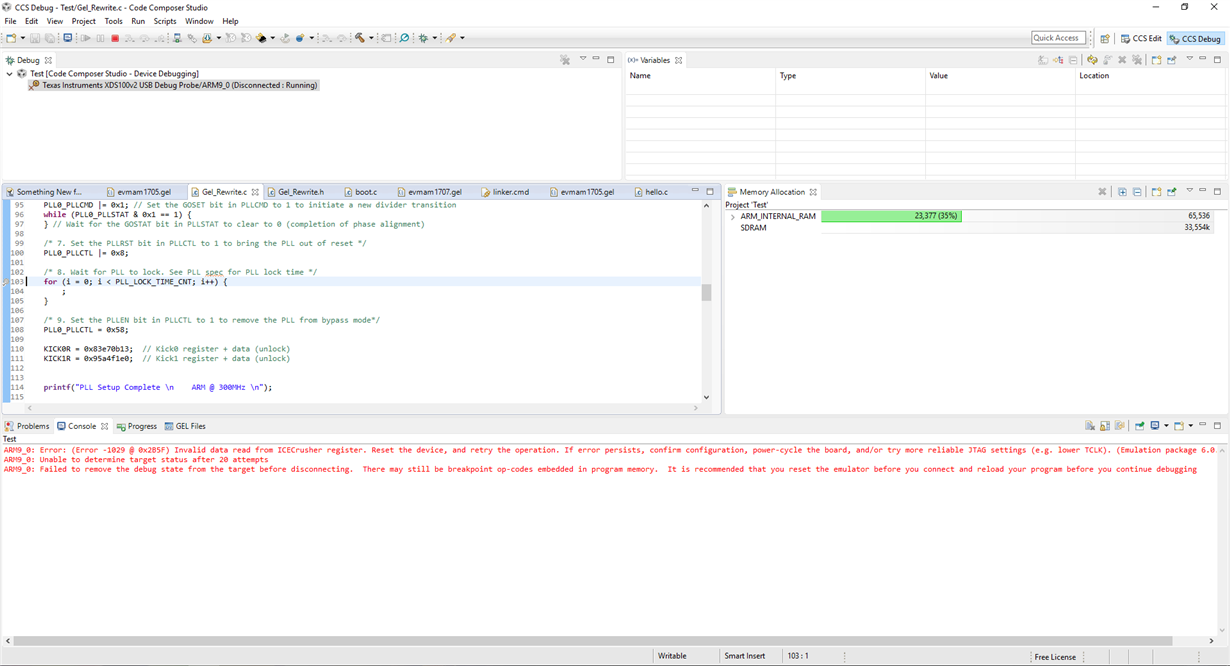

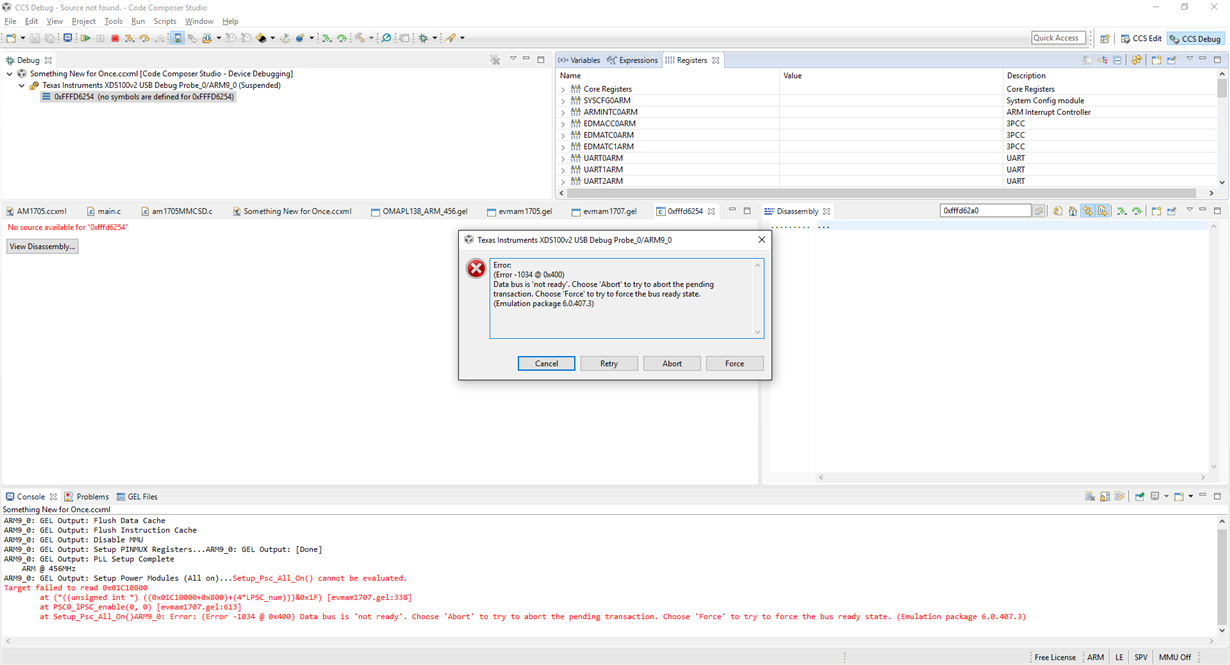

Here are the screenshots of the errors:

I have also tried converting the Gel script to a C file and building it as part of the project with little success. What I have noticed however is that it seems to be halting at different time nearly every time I run it which is making it quite hard to debug. Any help will be greatly appreciated.

I've attache the Gel Script belowevmam1705.gel