This time I have to address the boot – topic of C6747 (DA808, OMAP L137).

We use the master SPI boot process and the AIS format. Let me explain how we (I) do it.

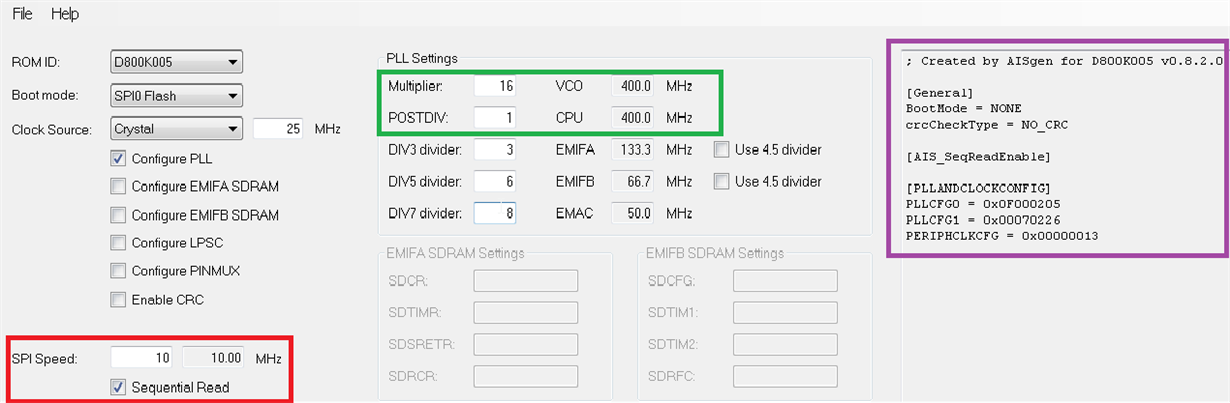

Creating the AIS image is done using the TI tool HexAIS_OMAP-L137 .

In order to speed up the boot time, on the very beginning of the load process we use so called “Pre-Defined ROM Functions” foreseen by TI (as described in the document SPRABB1C ).

For many years we have been using the separate ROM functions for DSP Core-Pll setup and SPI configuration:

For many years we (out of 8 available Pre-defined ROM functions) have used two functions:

- Function 0 (PLL Configuration)

setup via "OMAP-L137.ini" [PLLANDCLOCKCONFIG] section - Function 1 (Clock Configuration)

setup via "OMAP-L137.ini" [PERIPHCLKCFG] section

For some specific reason this solution is not suitable. Why?

- In C6000 core clock is used for generation of the peripheral clock SYSCLK2:

Fperipherals = SYSCLK2 = PLLOUT / DIV2 = PLLOUT / 2 - The clock rate for data format x can be calculated as follows:

SPI-Clock = SYSCLK2 / (PRESCALEx + 1) ...PRESCALEx determines the bit transfer rate of data format x if the SPI is the network master.

Well, if two configurations (mentioned above) are performed one after another (first core-Pll, then SPI) using separate commands, for a short time SPI (being configured afterwards) runs fast, too fast. Why?

Because it depends directly on the core-clock.

- Core clock of the DSP is set to some default value (SPI Master/25 MHz Quarz: 962 kHz).

- First ROM-function (“0”) is applied and peripheral clock (deriving from it) is of an undesired value (the command defining it comes yet, afterwards)

- Second ROM-function (“1”) gets fetched (using an irregular SPI inter-state) and executed; now SPI is set properly.

However, between steps 2 & 3 there’s an undesired ‘glitch’ of undefined state of SPI registers.

This topic is known to Texas Instruments very well.

For this reason, a special ROM command was implemented performing both setups (PLL and Clock Configuration) – at once! Using one ROM-function “5” only.

In the manual (SPRABB1C) this method is even the preferred one:

Function 5 (PLL and Clock Configuration)

setup via "OMAP-L137.ini" [PLLANDCLOCKCONFIG]

This function combines the PLL configuration and clock configuration functions into a single function call. This function takes three arguments.

The first two arguments match the arguments for the PLL configuration function, and the third argument matches the argument for the clock configuration function.

It is preferable to call this function when the I2C, SPI, or UART modes are being used rather than calling the PLL configuration and clock configuration functions separately; since it ensures that the system PLL and the peripheral's clocks are changed together.

I immediately knew it was the solution to preventing the ‘glitch’.

Unfortunately, for some reason my application does not start if I use this method (function “5”).

The boot process gets finished, but DSP application cannot run.

I assume some problems with the DSP PLL.

Returning the boot method to initial approach (using separate functions 0 & 1) causes application to boot successfully again. However having an unwanted SPI ‘glitch’ in between.

So finally my question:

- What could be the reason Pre-defined Boot ROOM “5” couldn’t work?

- Where could I find some more details on function “5” internal behavior?

I’ve tried to add the delay (“PLL_LOCK_TIME_CNT”) after PLL-setup, but it didn’t help.

Additionally, I removed the PLL-setup in the application (since PLL is already configured in the process of booting), bit this neither helped.

Many thanks for your support!

Regards from Vienna,

Mladen

Appendix:

AIS File Containing

Command OpCodes

0x41504954, MAGIC WORD ('T','I','P','A')

0x58535963, Function Sequential Read Enable Command (without sending READ-command for each byte)

0x5853590D, Function Execute Command (DSP-Inits prior to load process)

0x00030005, ARG CNT (3) & FXN NUM (5 = PLL and Clock Configuration)

0x10000205, PLLCFG0: PLLM=0x10, POSTDIV=0 (/(0+1)), PLLDIV3 (for EMIFA), PLLDIV5 (for EMIFB)

0x00070800, PLLCFG1

0x00000014, SYSCLK2 of 200 MHz / PRESCALE of 0x14 ie. 20 => 10 MHz SPI-Clock

0x58535903, ENABLE_CRC_COMMAND

0x58535901, SECTION_LOAD_COMMAND

0x11800000, Section start-address (section: .text)

0x00006900, Section-Length [Bytes]

. . . . .