Hi ,

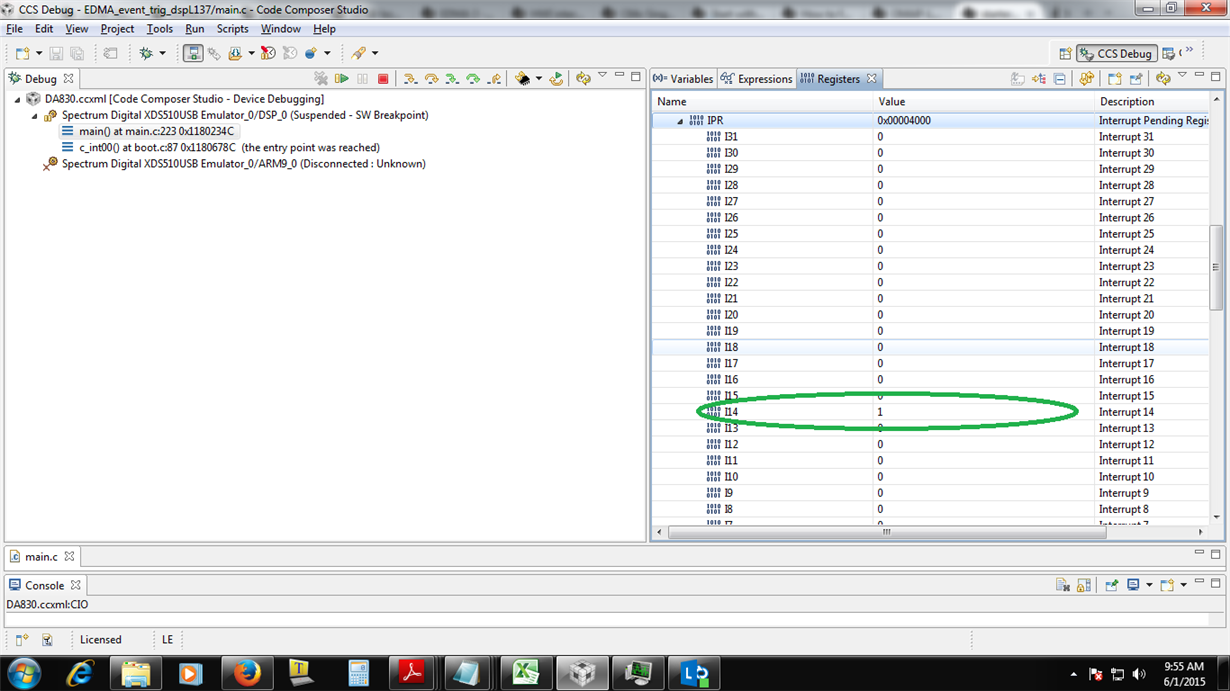

I am using TMS320C6745 and trying to use EDMA with SPI_1, but I am unable to get the IPR bit for SPI_1.

I am setting the SPI bit for DMA request enable also

spiRegs->SPIINT0 |= ( 1 << 16 ); // DMA Request Enabled

I am doing the following setting for EDMA:

static void setup_EDMA (void)

{

// Clear Event Registers

CSL_FINST(edma3ccRegs->ECR, EDMA3CC_ECR_REG, MASK);

CSL_FINST(edma3ccRegs->SECR, EDMA3CC_SECR_REG, MASK);

// Enable Channel 18 to DSP (Region 1)

CSL_FINST(edma3ccRegs->DRA[CSL_EDMA3_REGION_1].DRAE,

EDMA3CC_DRAE_E18, ENABLE);

// Assign Channel 18 to Queue 0

CSL_FINST(edma3ccRegs->DMAQNUM[1], EDMA3CC_DMAQNUM_E2, Q0);

// Initialize PaRAM Transfer Context for Event 18

init_PaRAM_event18();

// Enable Channel 18 Event Register

CSL_FINST(edma3ccRegs->EESR, EDMA3CC_EESR_E18, SET);

// Enable Interrupts for Channel 18

CSL_FINST(edma3ccRegs->IESR, EDMA3CC_IESR_I18, SET);

}/* setup_EDMA */

Please suggest me if any mistake I am doing while the configuration.

Regards,

Arvind