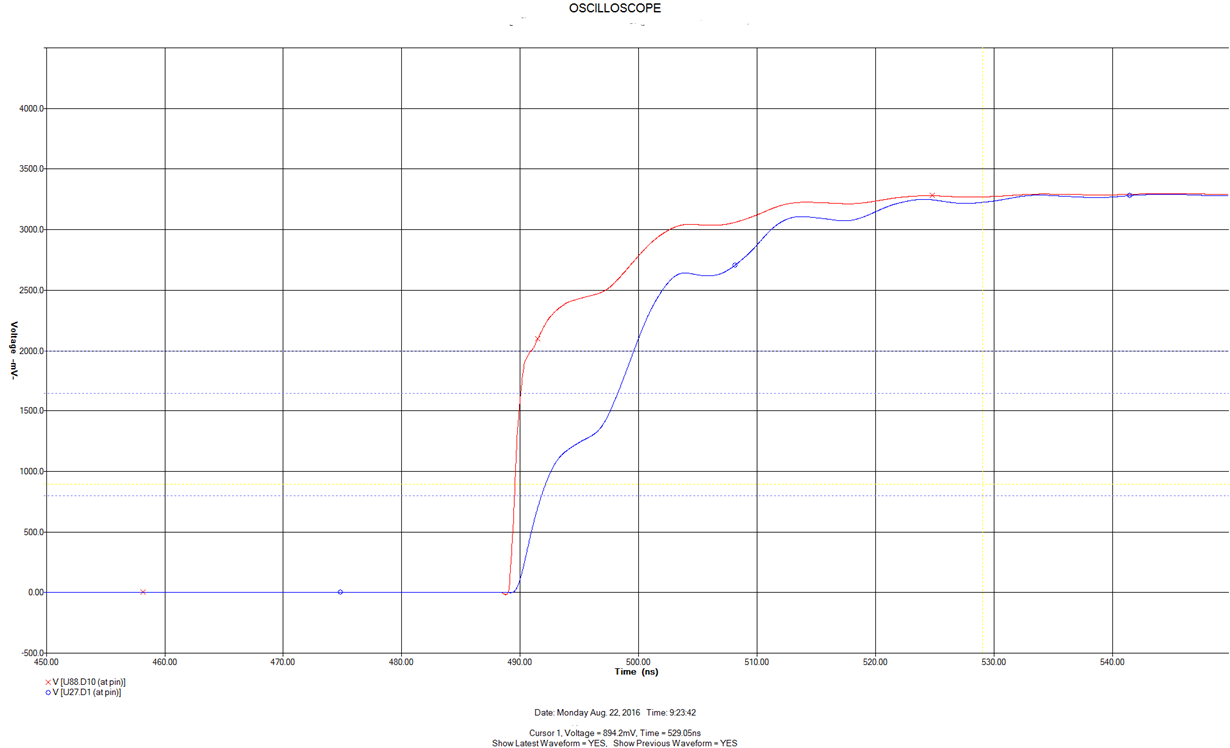

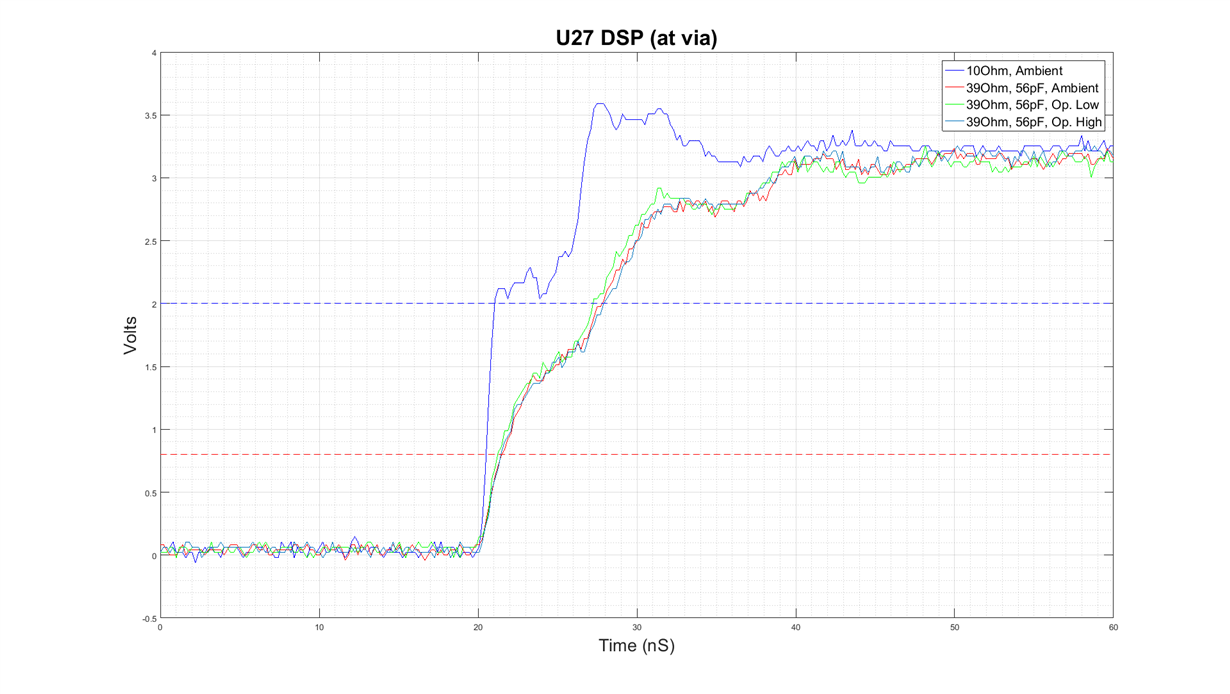

I have one of the C64x series DSPs on a board and found a trace with a less than ideal clock edge. We are in the process of testing a modification to the trace but wanted to get TIs input on the acceptability of the signal.

In the data sheet it specifies that the clock needs to be monotonic in nature, but we were curious to know if there are slope limits to the clock edge that must be met.

Customer has document with details of simulations and scope captures but cannot share publicly.