Tool/software: Code Composer Studio

- FPGA configuration procedure:

- Initialization procedure: HPIC configuration , write 16‘h0060 to HPIC twice;

- HPIA configuration , write address 32’h80010000 to HPIA (the first half-word is 16’h8001, the second half-word is 16’h0000) ;

- Write data to HPID (first 16bit and then next 16bit);

- Step 2&3 loop.

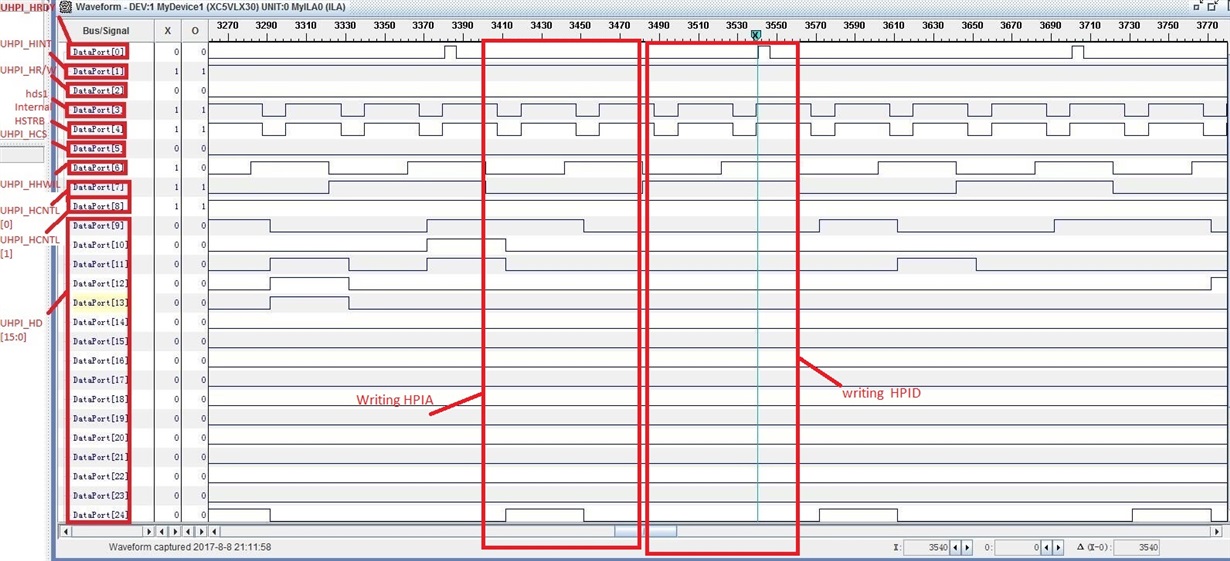

Figure1

As shown in the figure 1 ,

port0 is the DSP’s feedback :UHPI_HRDY;

port1 is the DSP’s feedback :UHPI_HINT;

port2 is the FPGA part’s output: UHPI_HR/W, the value is 0, meaning write operation;

port3 is the FPGA part’s output: hds1, and value of hsd2 is 1;

port4 is the simulation on FPGA of DSP internal signal: Internal HSTRB ,when UHPI_HCS equals 0, Internal HSTRB equals hds1;

port5 is the FPGA part’s output: UHPI_HCS,the value is 0;

port6 is the FPGA part’s output: UHPI_HHWIL;

port[8:7] are the FPGA part’s output : UHPI_HCNTL[1:0];

port[24:9] are the inout : UHPI_HD[15:0].

question:

When writing the HPIC, it works correctly. The value has been written into the DSP register (can be seen from CCS)

But, when writing the HPIA, the DSP seems does not acknowledge the write operation (the UHPI_HRDY keeps low). So HPIA is not written correctly.

Then, when writing the HPID, the DSP acknowledges (UHPI_HRDY rise at the 2nd half word, then falls to low again). But the value is not written into the RAM address, since HPIA is not correct.

So, our question is why the timing of HPIC and HPID is right, but HPIA cannot be written.

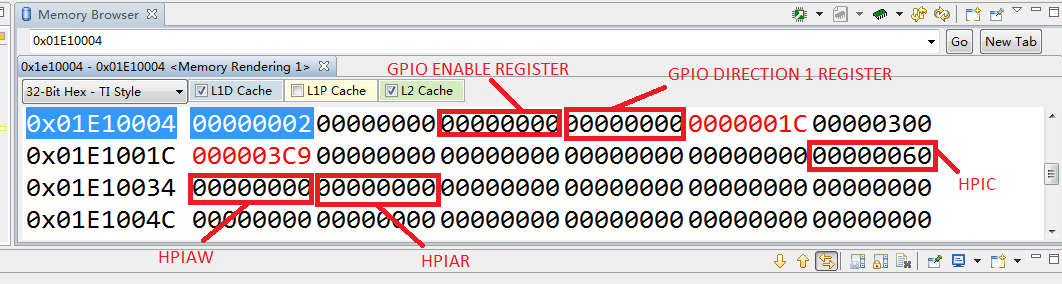

DSP configuration :

Figure2

0x01E1000C is GPIO ENABLE REGISTER, equals 0, which means the function of HPI

0x01E10010 is GPIO DIRECTION 1 REGISTER, setting to 0, which means HD is the DSP’s input

0x01E10030 is HPIC, can be written in normally.

0x01E10034 is HPIAW, can’t be written in.

0x01E10038 is HPIAR, can’t be written in

PINMUX_REG_13/PINMUX_REG_14 PINMUX_REG_15 PINMUX_REG_16 enable the function of HPI

HPIENA of CFGCHIP1 has enabled, HPIBYTEAD is set to word address(byte address has also been set once)

note:the clk of HPI on FPGA is 40M, chipscope sampling clk is 200M; the clk of HPI on DSP is 40M 75M.