Tool/software: TI-RTOS

Hi,

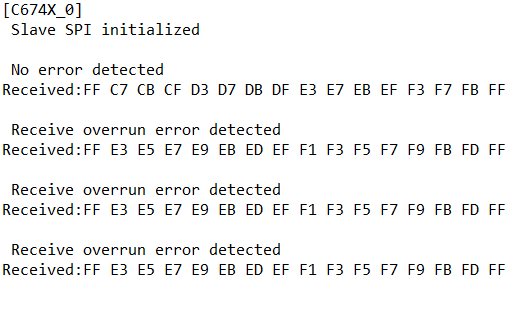

I am using the following platform Tm320C6748 running DSP BIOS 5, (Custom Board) and PSP drivers 01_30_01

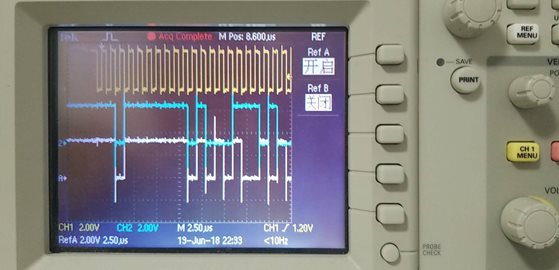

I configured the SPI in slave mode, operation mode is interrupt mode.

seems that SPI tx interrupt continuously triggered even before I write anything to the transmit buffer.

Once SPI is ebabled tx interrupt is triggered.

any suggestions why the tx interrupt triggers ?

Alex Levit.