Dear All,

I have a question about using C6748's SPI1 as SPI Slave.

I can successfully receive data from SPI Master. However, I failed to correctly send data to it.

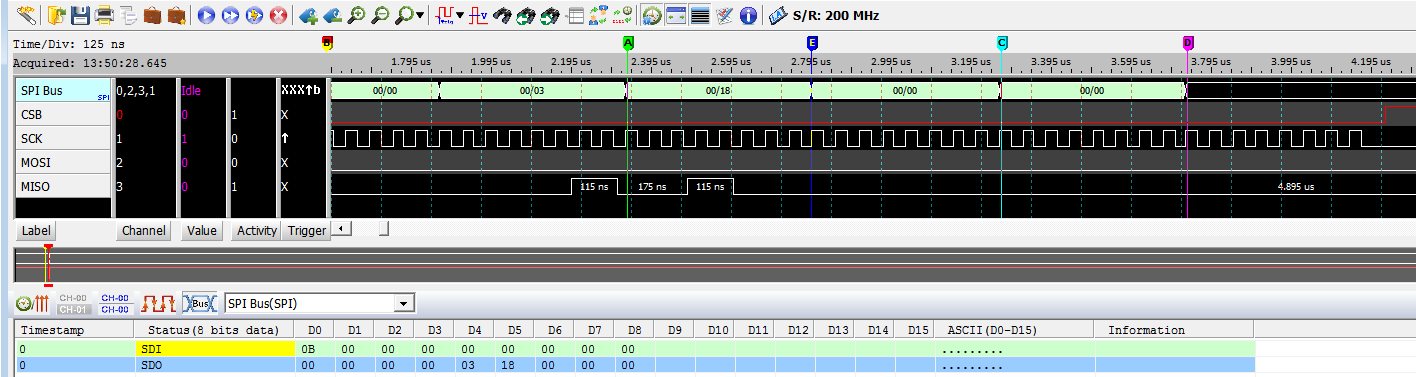

What I expect to send on MISO is:

63_21_43_65 => 0110_0011_0010_0001_0100_0011_0110_0101

6 3 2 1 4 3 6 5

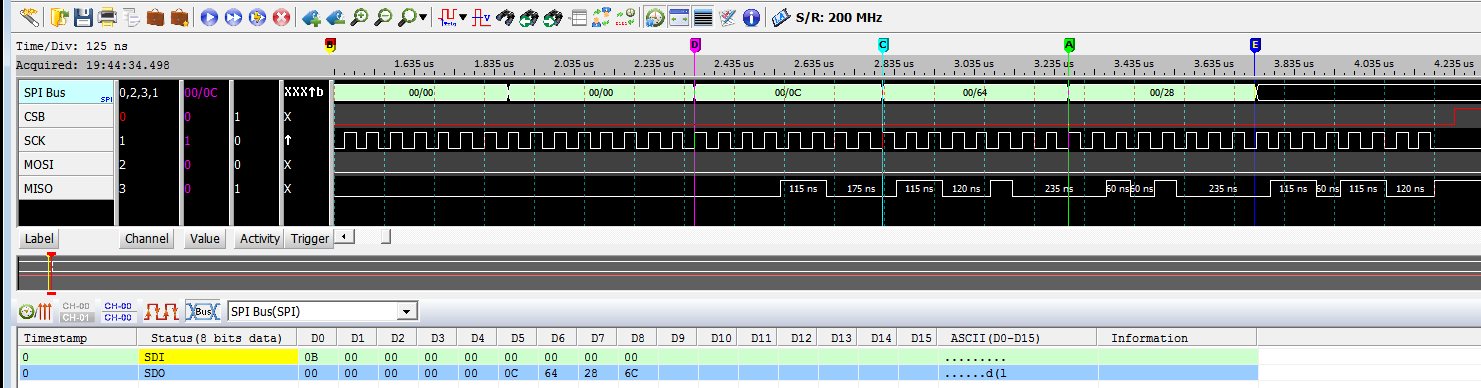

But it turns out the actual waveform on MISO is:

0C_64_28_6C => 0000_1100_0110_0100_0010_1000_0110_1100

0 C 6 4 2 8 6 C

The waveform seem to have 3-bit "delay" (The 3 zero highlighted in red) compared to what I expected.

You can see the waveform here:

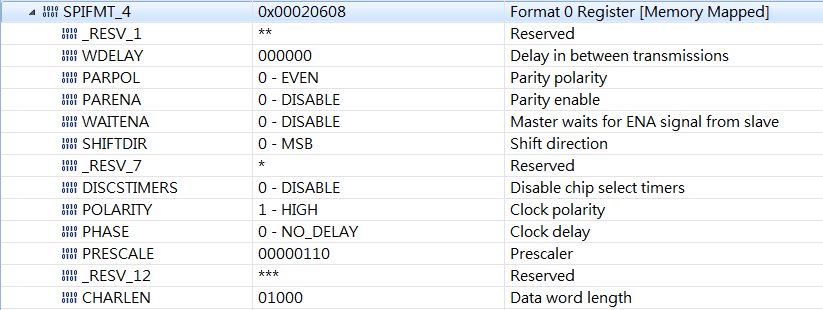

And you can see the settings of the SPIFMT0 register here:

Originally I assume that if my FW sends data too late, then the delay on MISO will be "byte-aligned", i.e.,

delay will be 1-byte, 2-byte, etc. However, it seems that my assumption is not correct, right?

Any comment will be highly welcome!

Regards,

Oliver