Hi there

I'm using TMS320C6746 and tring to do test about UPP Peripheral (Loopback test)

before i initialize the UPP, I have done pll, psc setting and pin multiplexing setting

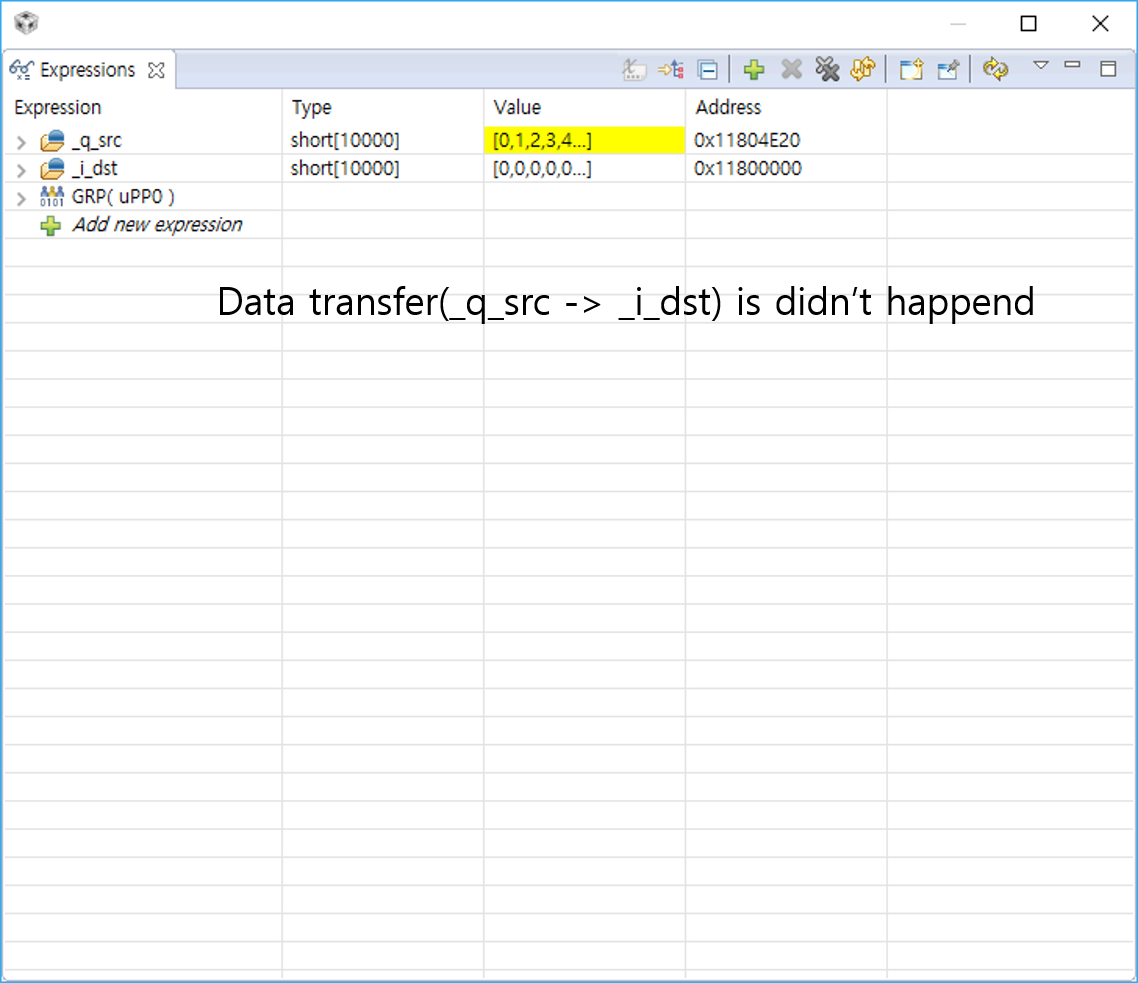

but it seems i did something wrong

i attached my source code about the UPP

could you give me a hand?

int16_t _q_src[10000];

int16_t _i_dst[10000];

void upp_init(void)

{

int32_t i = 0;

int16_t temp_data = 0;

int16_t upper_data_limit = 2047;

int16_t lower_data_limit = -2048;

memset((void*)_q_src, 0x00, sizeof(_q_src));

memset((void*)_i_dst, 0x00, sizeof(_i_dst));

while(temp_data < upper_data_limit)

{

_q_src[i] = temp_data;

temp_data++;

i++;

}

while(temp_data > lower_data_limit)

{

_q_src[i] = temp_data;

temp_data--;

i++;

}

while(temp_data < 0)

{

_q_src[i] = temp_data;

temp_data++;

i++;

}

// poll the DB bit to make sure the DMA is idle

while(CSL_FEXT(upp0Regs->UPPCR, UPP_UPPCR_DB));

CSL_FINST(upp0Regs->UPPCR, UPP_UPPCR_SWRST, RESET);

for(i = 0; i < 200; i++);

CSL_FINST(upp0Regs->UPPCR, UPP_UPPCR_SWRST, RUNNING);

upp0Regs->UPCTL = CSL_FMKT(UPP_UPCTL_DPFB, RJSE) |

CSL_FMKT(UPP_UPCTL_DPWB, 12BIT) |

CSL_FMKT(UPP_UPCTL_IWB, 16BIT) |

CSL_FMKT(UPP_UPCTL_DRB, SINGLE) |

CSL_FMKT(UPP_UPCTL_DPFA, RJSE) |

CSL_FMKT(UPP_UPCTL_DPWA, 12BIT) |

CSL_FMKT(UPP_UPCTL_IWA, 16BIT) |

CSL_FMKT(UPP_UPCTL_DRA, SINGLE) |

CSL_FMKT(UPP_UPCTL_DDRDEMUX, DISABLE) |

CSL_FMKT(UPP_UPCTL_SDRTXIL, DISABLE) |

CSL_FMKT(UPP_UPCTL_CHN, TWO) |

CSL_FMKT(UPP_UPCTL_MODE, DUPLEX0);

upp0Regs->UPICR = CSL_FMKT(UPP_UPICR_TRISB, DISABLE) |

CSL_FMKT(UPP_UPICR_CLKINVB, NORMAL) |

CSL_FMK(UPP_UPICR_CLKDIVB, 11) |

CSL_FMKT(UPP_UPICR_WAITB, DISABLE) |

CSL_FMKT(UPP_UPICR_ENAB, DISABLE) |

CSL_FMKT(UPP_UPICR_STARTB, ENABLE) |

CSL_FMKT(UPP_UPICR_TRISA, DISABLE) |

CSL_FMKT(UPP_UPICR_CLKINVA, NORMAL) |

CSL_FMK(UPP_UPICR_CLKDIVA, 11) |

CSL_FMKT(UPP_UPICR_WAITA, DISABLE) |

CSL_FMKT(UPP_UPICR_ENAA, DISABLE) |

CSL_FMKT(UPP_UPICR_STARTA, ENABLE);

upp0Regs->UPIVR = CSL_FMK(UPP_UPIVR_VALB, 0x0000) |

CSL_FMK(UPP_UPIVR_VALA, 0x0000);

upp0Regs->UPDLB = CSL_FMKT(UPP_UPDLB_BA, ENABLE) |

CSL_FMKT(UPP_UPDLB_AB, DISABLE);

CSL_FINST(upp0Regs->UPPCR, UPP_UPPCR_EN, ENABLE);

upp_loopback(_q_src, _i_dst, sizeof(_q_src));

}

void upp_loopback(int16_t *q_src, int16_t *i_dst, uint16_t length)

{

// IDMA Channel Q

upp0Regs->UPQD0 = CSL_FMK(UPP_UPQD0_ADDRH, (uint32_t)q_src);

upp0Regs->UPQD1 = CSL_FMK(UPP_UPQD1_LNCNT, 1) |

CSL_FMK(UPP_UPQD1_BCNTH, length);

// IDMA Channel I

upp0Regs->UPID0 = CSL_FMK(UPP_UPID0_ADDRH, (uint32_t)i_dst);

upp0Regs->UPID1 = CSL_FMK(UPP_UPID1_LNCNT, 1) |

CSL_FMK(UPP_UPID1_BCNTH, length);

}