Other Parts Discussed in Thread: DAC7742, DAC902

Dear Champs,

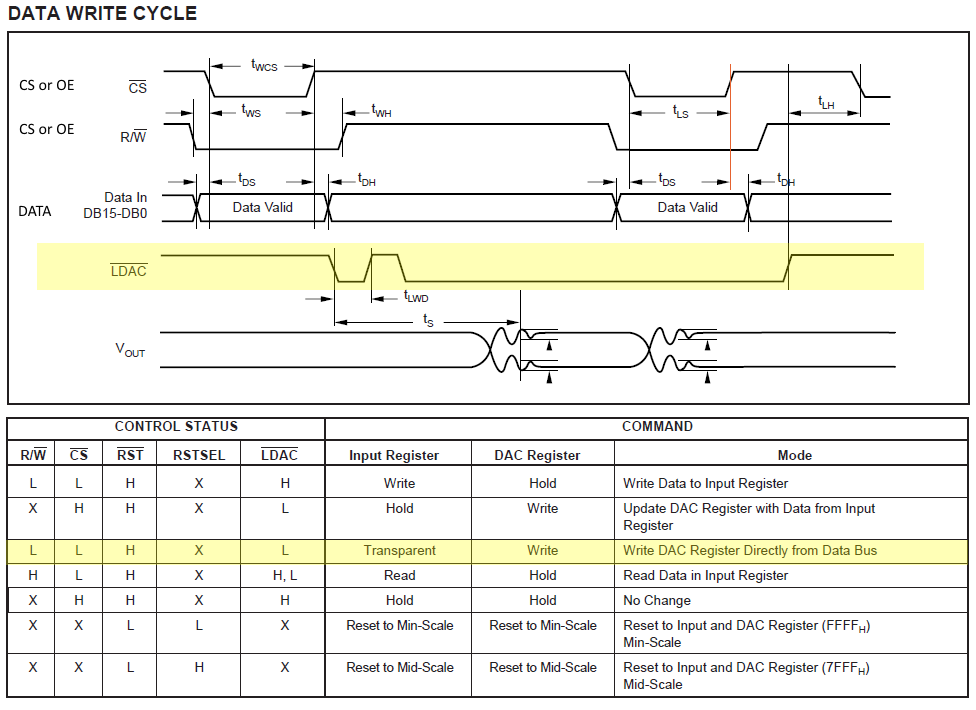

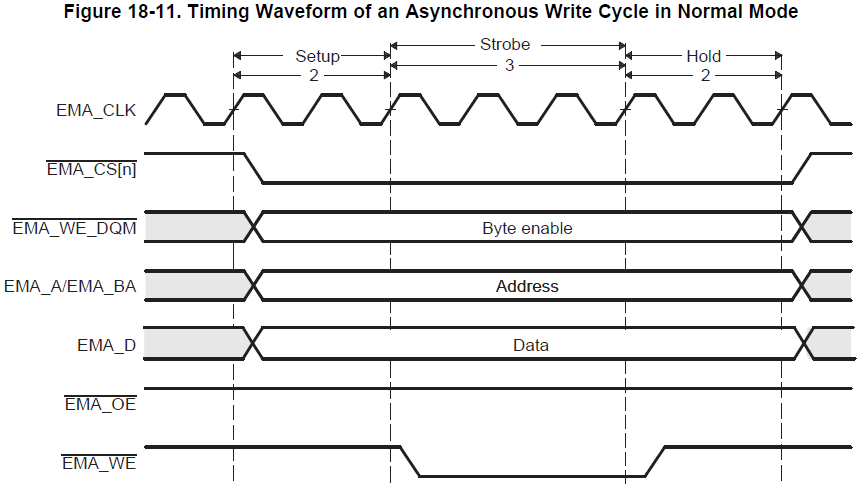

Is it possible to connect DAC to EMIF of C6748 and transmit data to DAC continuously?

As 2ch ADC were connected to 2ch upp of C6748, I think there is only EMIF port to connect DAC and I think DAC was connected to EMIF in async mode, but I don't confident how EMIF can send waveform data to DAC continuously in async mode during a minute.

Please help to check if EMIF can work with DAC to send waveform data during some time.

Thanks and Best Regards,

SI.