Hi,

I am having an issue with waking up the CPU to run a task after a post from an HWI.

BIOS: 6.41.00.26 (issue also seen in 6.40.02.27)

Processor: MSP430F5437A

Compiler: MSP430 4.3.3

CCS: 6.0.1.00040

Description:

I have an HWI setup to transmit and receive bytes via I2C of USCI_B and a Task that sends the start condition and pends for the last byte to be transmitted/received and a stop condition to be sent. Once the HWI routine sends the stop condition, it will do a post to the Task such that the Task can continue on.

The system operates in LPM2 and CPU Idle has been enabled so that during TX/RX of the I2C, the CPU will switch to LPM2 until the I2C triggers a TX/RX interrupt or post to the Task.

Issue:

The issue is, after the stop condition has been sent, a post to the task and the HWI exits, the pending task does not run and so the system remains in Idle waiting for another interrupt. If another interrupt occurs, the CPU will wake up, service the interrupt and the Task that was suppose to run previously, will run.

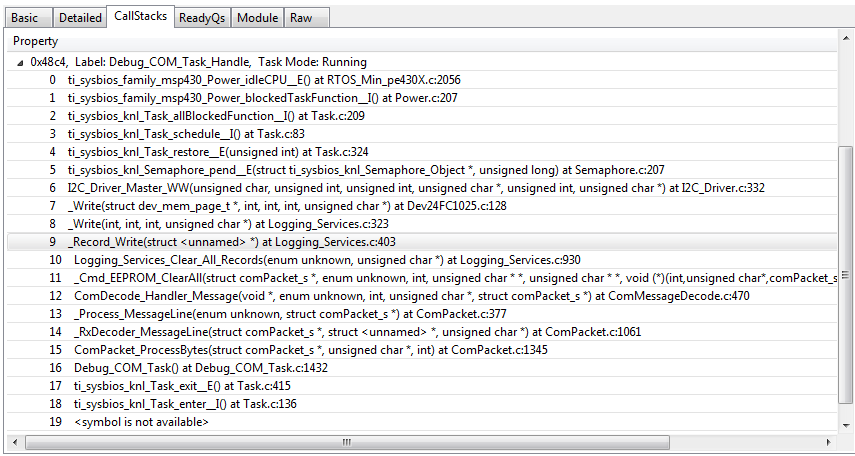

I took a look at the ROV when the CPU is in Idle after the post to the Task and it shows from the callstack that the Task is indeed in the "Running" mode. However it also shows that the

ti_sysbios_knl_Task_allBlockedFunction_I()

has been called. Can I assume that SYS/BIOS calls this function when it determines that no tasks are able to run and thus transitions the CPU to the Idle state? The ROV also shows that the Task's stack has not peaked or overflowed.

Notes:

- This issue manifested when I ramped MCLK up from default 8.192 MHz (DCO divide 2) to 16.384 MHz. I made sure to set the VCore to the appropriate level to accomodate this change. Under 8.192 MHz the issue is not observed.

- The data transmitted/received on the I2C is verified to be correct.

- When adding a small delay, __delay_cycles(100) which under 16.384 MHz works out to be roughly 6.1 microseconds, to the start of the HWI the issue goes away.

- Calling the Power_wakeCPU() function after the post to the task within the HWI does not resolve the issue.

Thanks for looking into this issue,

Bryon