Test conditions: I2C speed of 400KHZ.

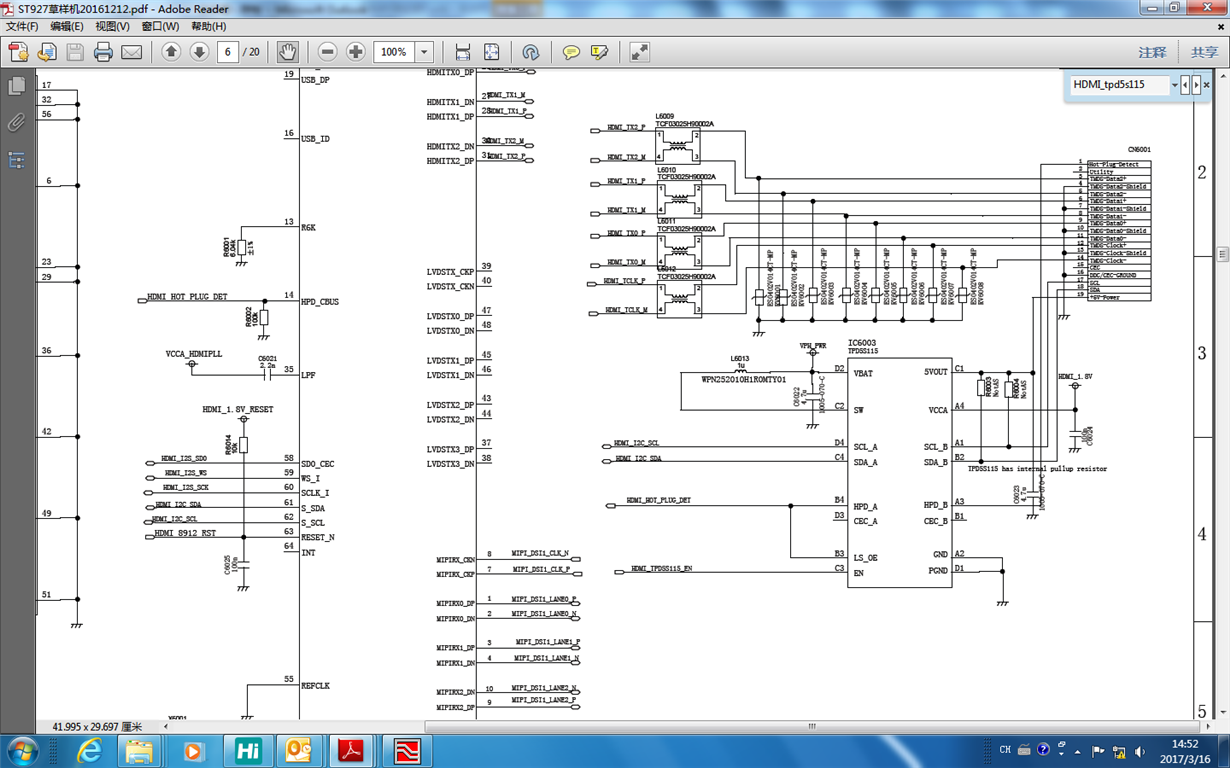

Pull the A-side HPD_A up to 1.8V and the handset AP sends an I2C instruction to test the SCL_A / SDA_A / SCL_B / SDA_B-side waveform (B-side HDMI terminal is floating and not connected).

The problem is:

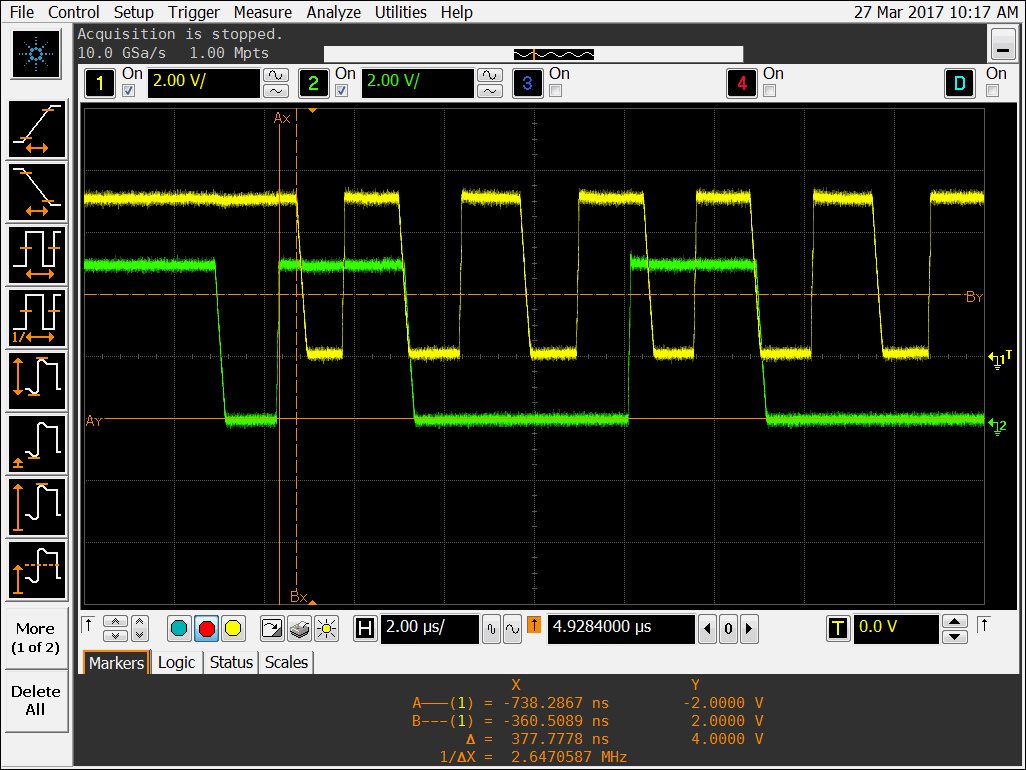

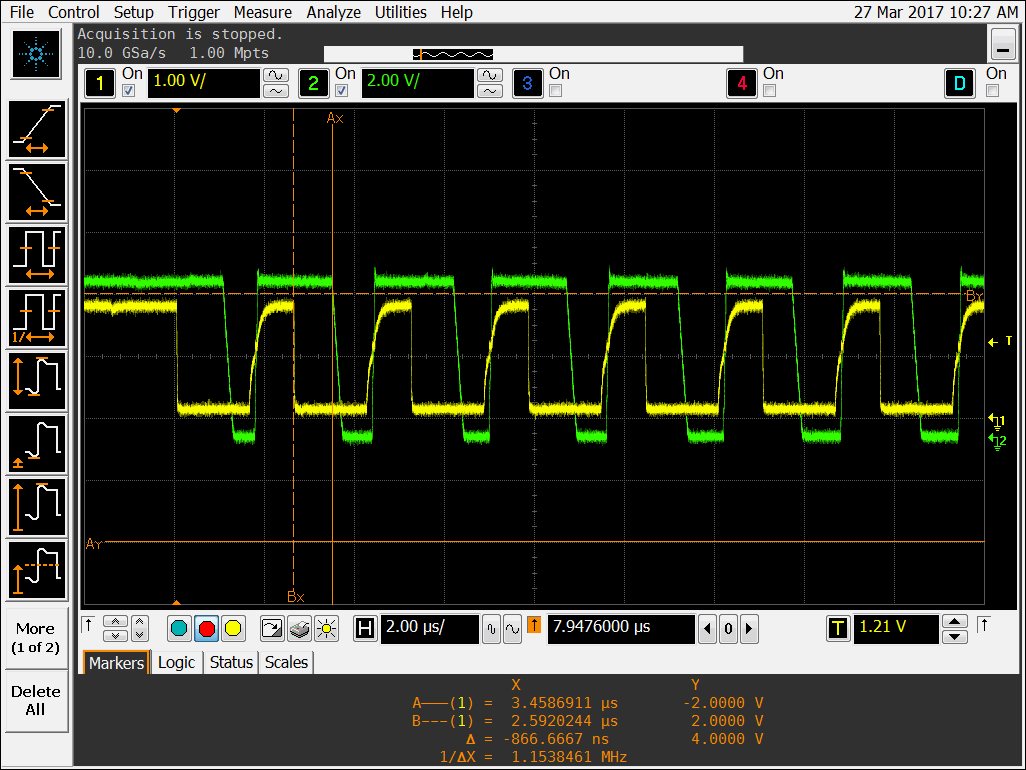

1. SCL_B is delayed by about 800 ns compared to the falling edge of SCL_A. (Refer to 1.8v-5v-scl.bmp)

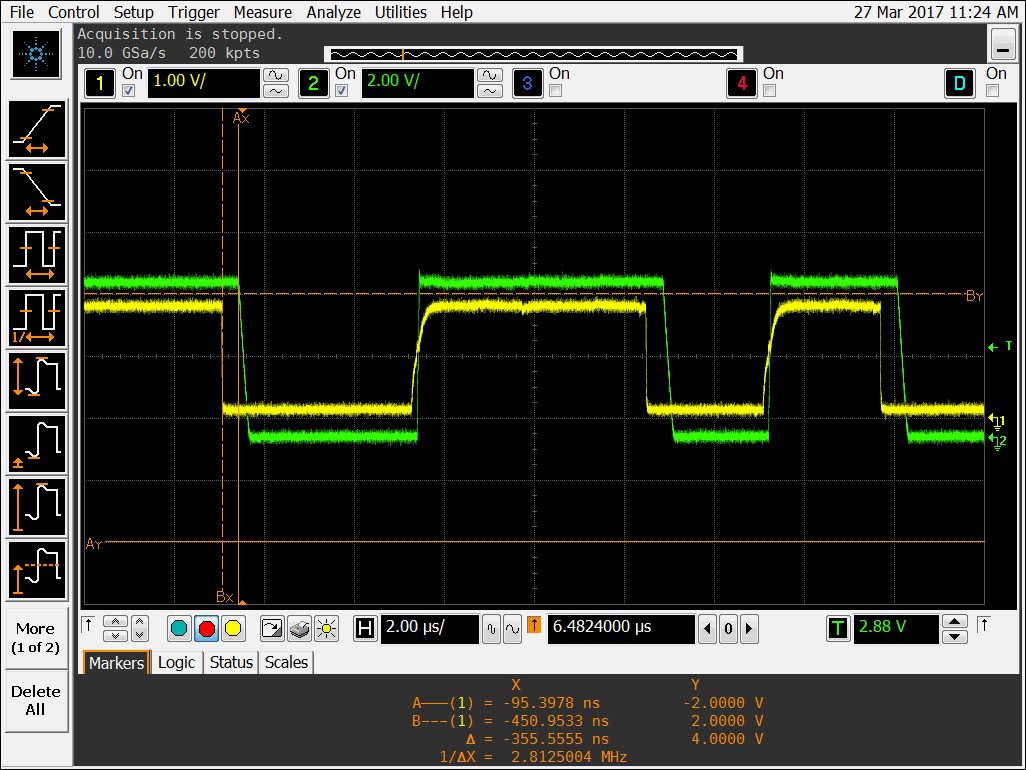

2, SDA_B is delayed by about 350ns compared to SDA_A falling edge. (Refer to 1.8v-5v-sda.bmp)

While the normal value of the specification value of 370ns, that is, SDA is in line with the specifications of the book, but the SCL does not meet, and the difference is more.

Because the delay of SCL will cause problems with B-side I2C timing. (Refer to 5v-scl-sda.bmp)