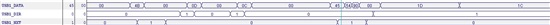

I am using two of these PHYs back to back through a FPGA. One playing Peripheral and the other Host. On the Host port I have a memory stick and on the Peripheral port a Windoze PC and both are operating at High Speed.

I get a significant number of resets [1] and then communication stops with either device randomly stuck with DIR high and Data of x"1c" (NXT and STP are both low)

Is there any reason why either should ever lock up in this state?

[1] From SE0 being applied continuously for more than 3ms and not to be confused with a hardware reset.