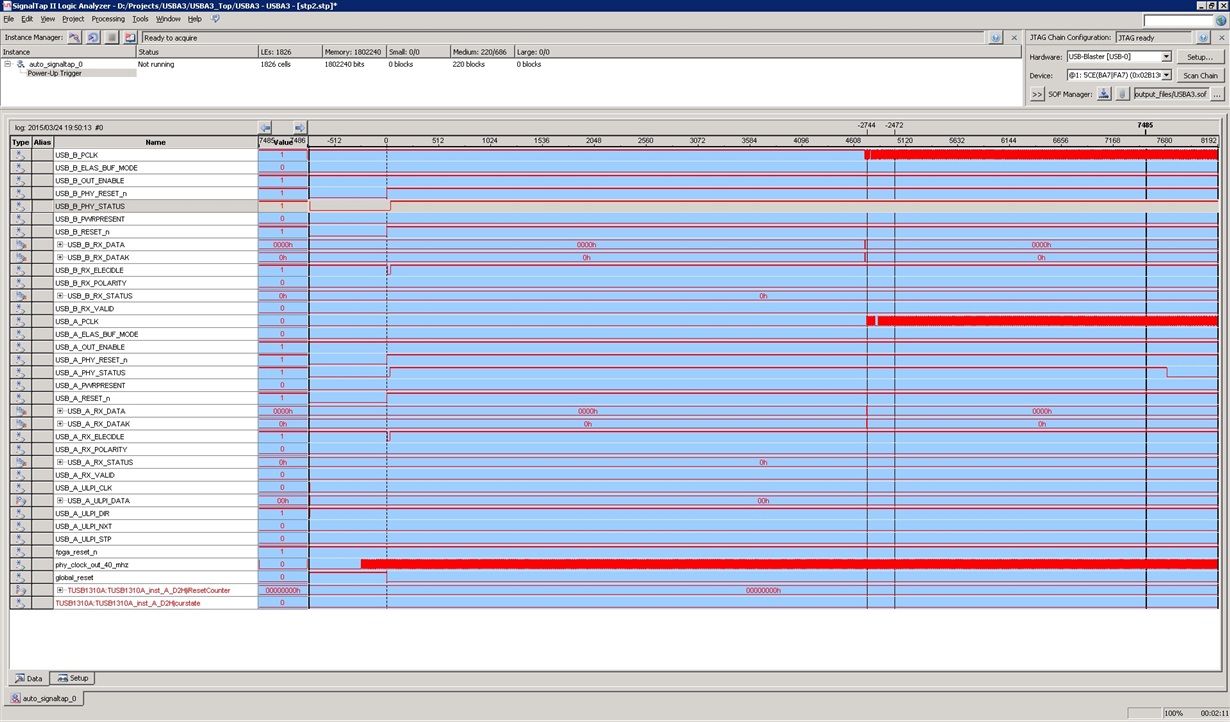

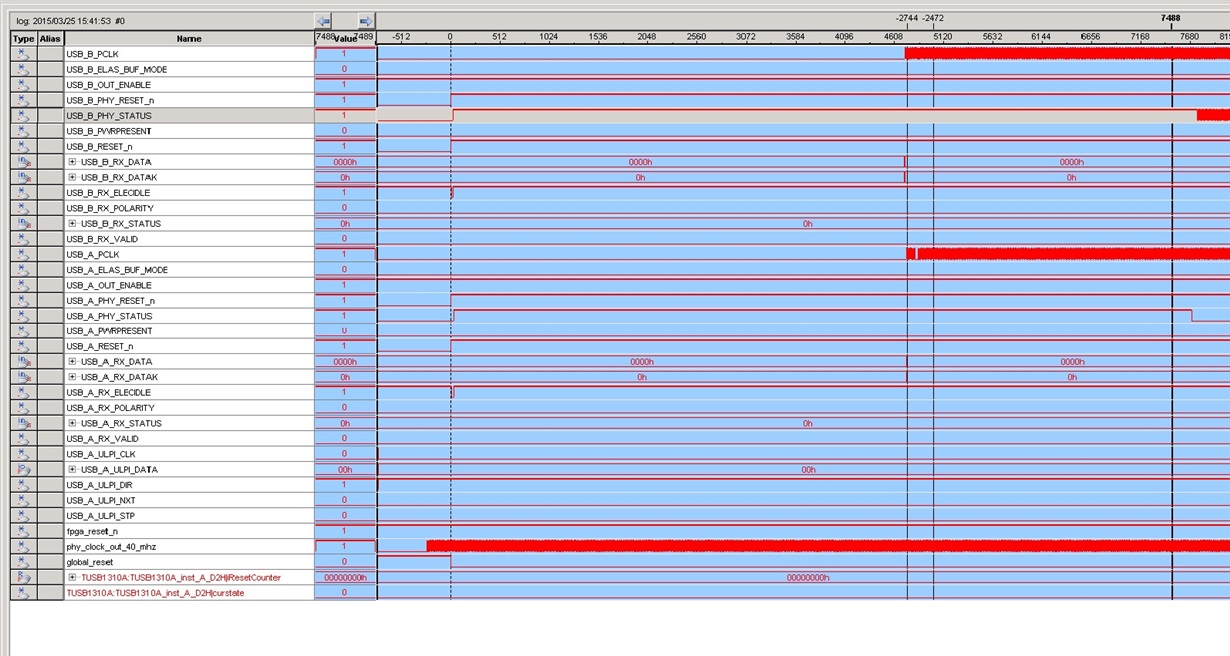

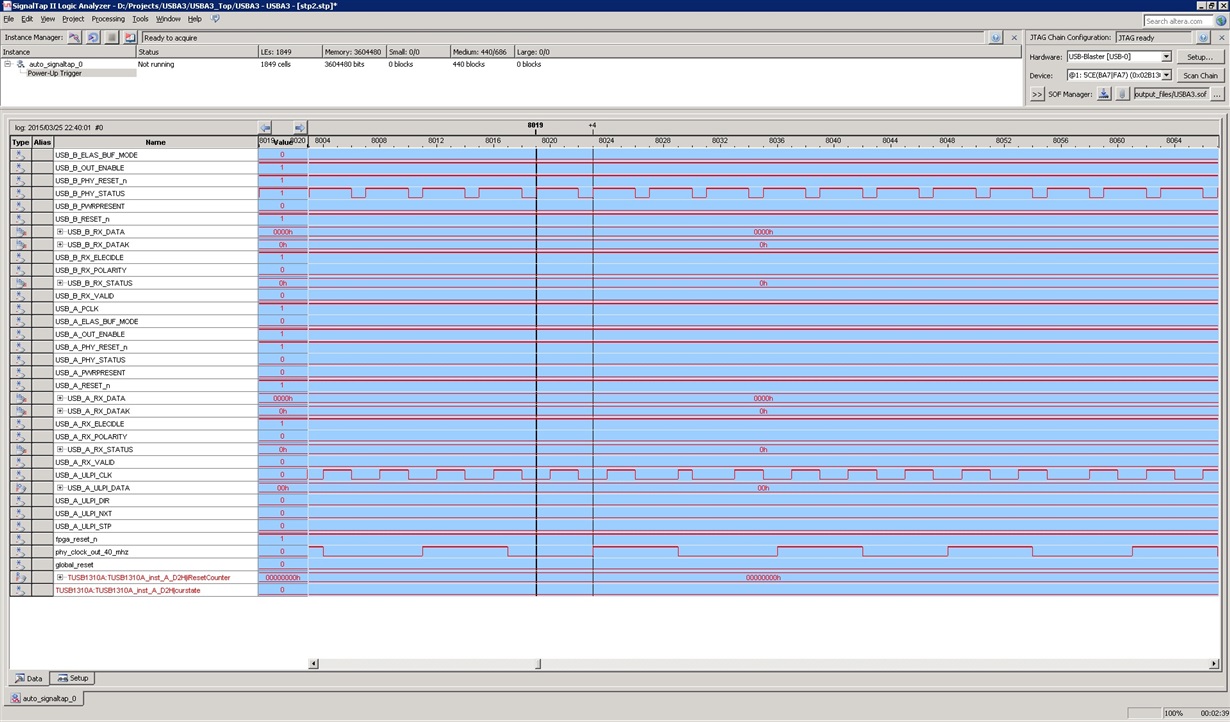

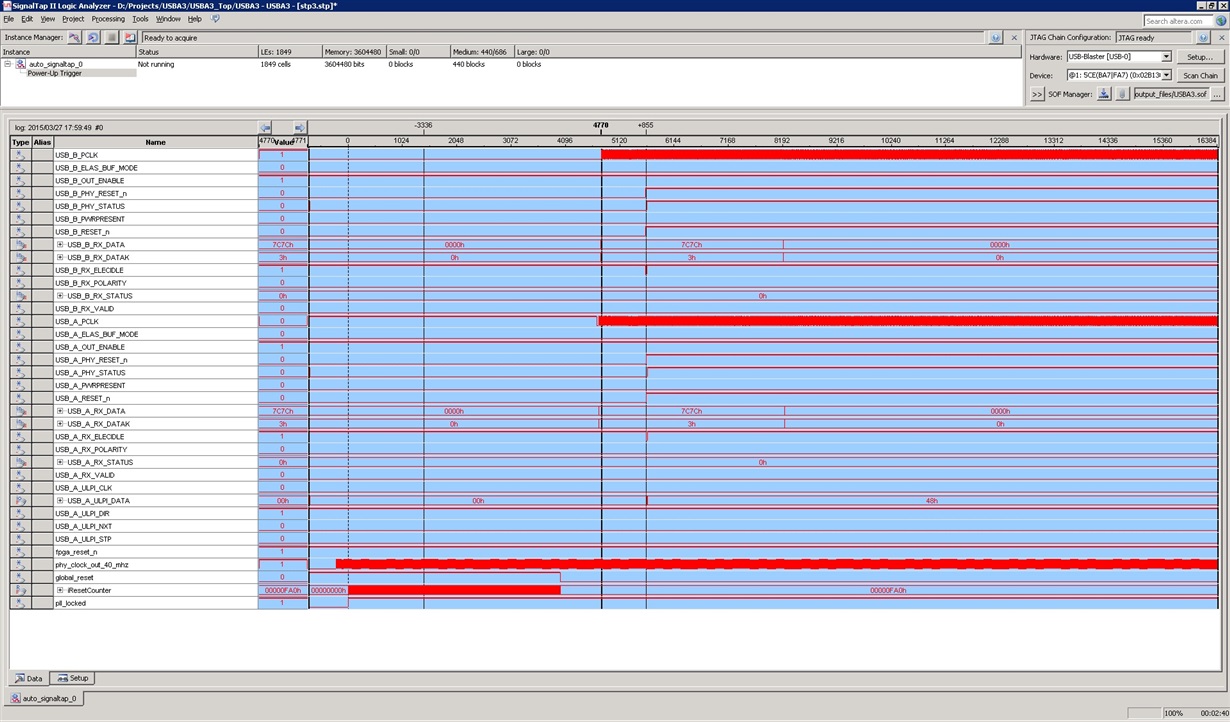

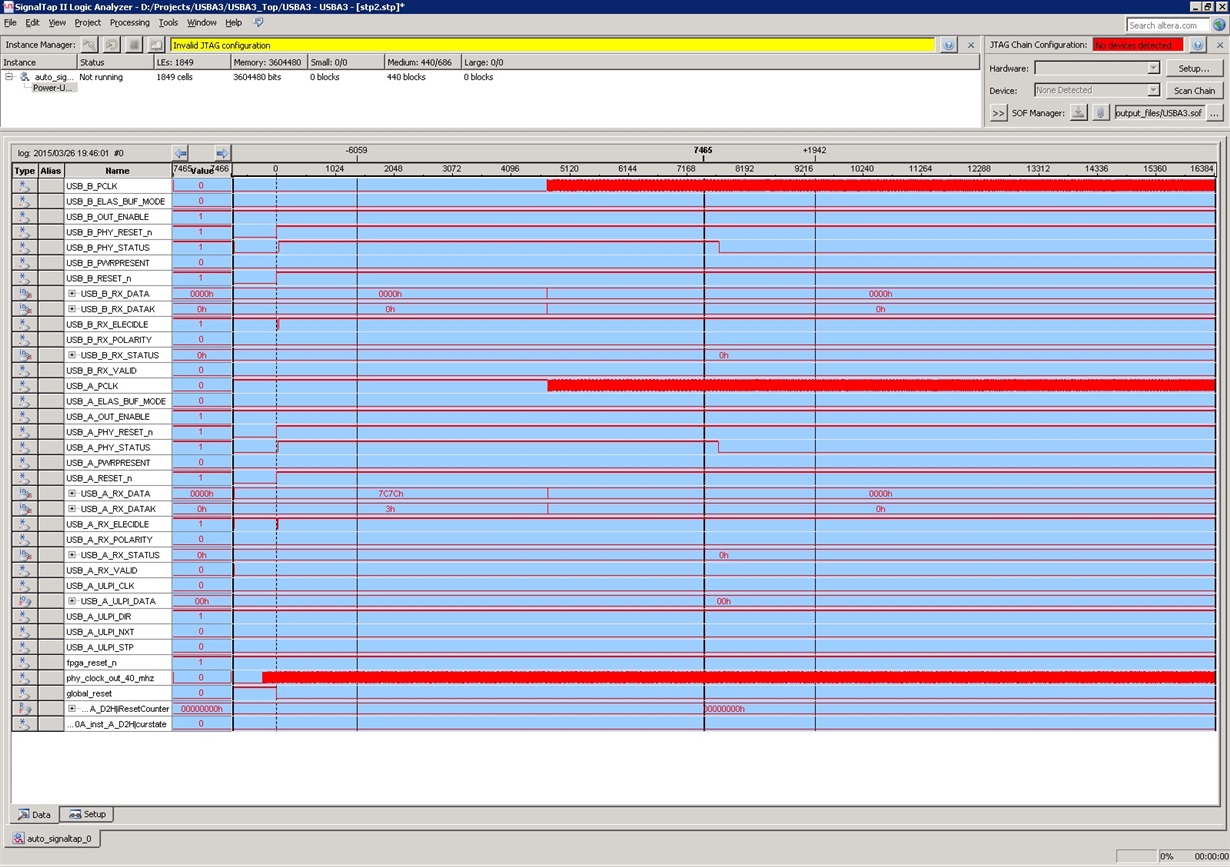

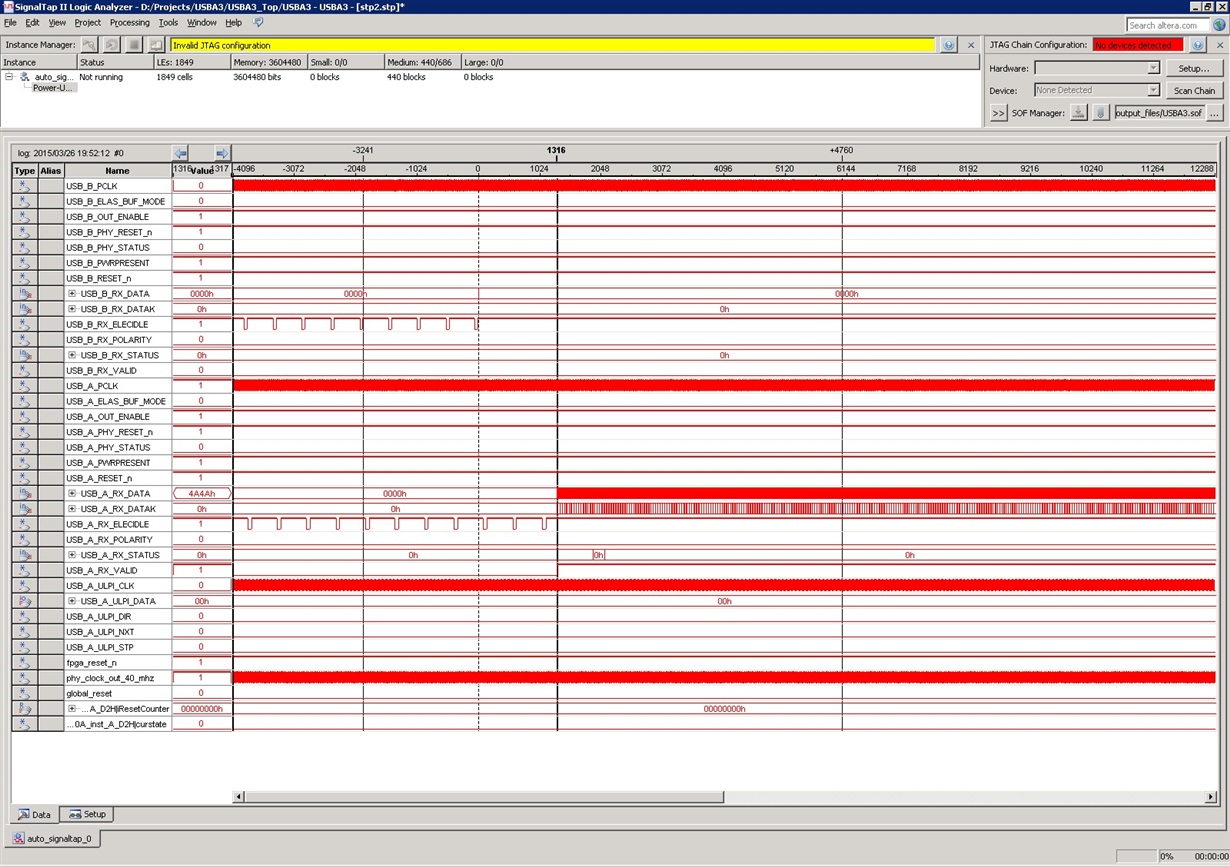

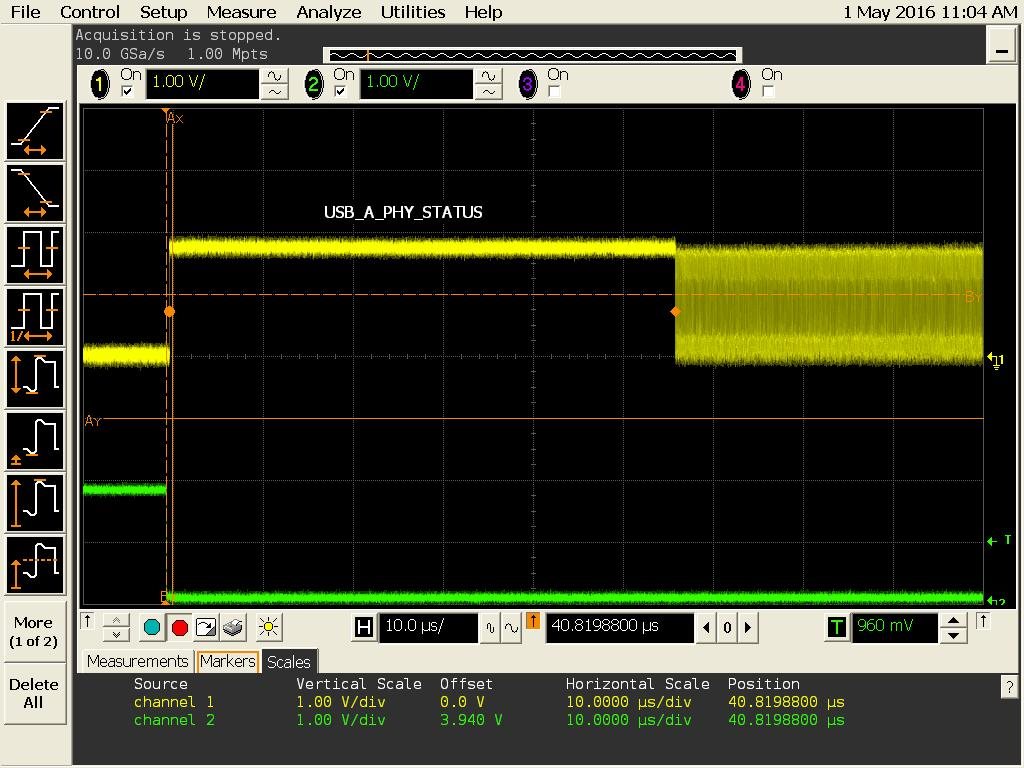

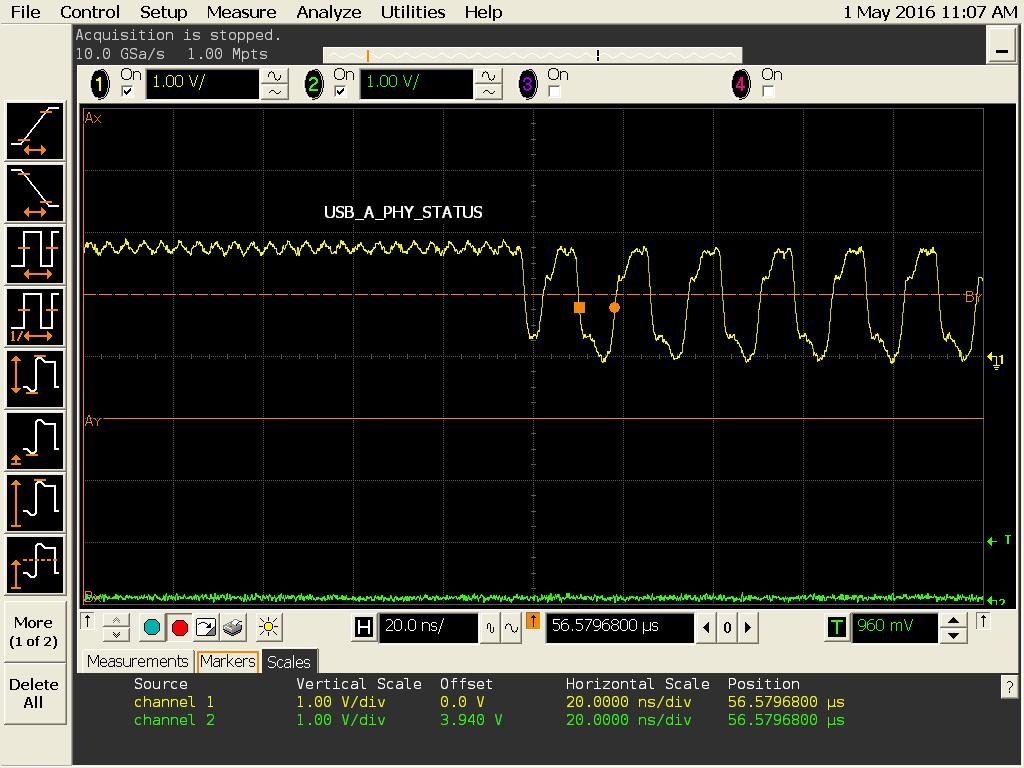

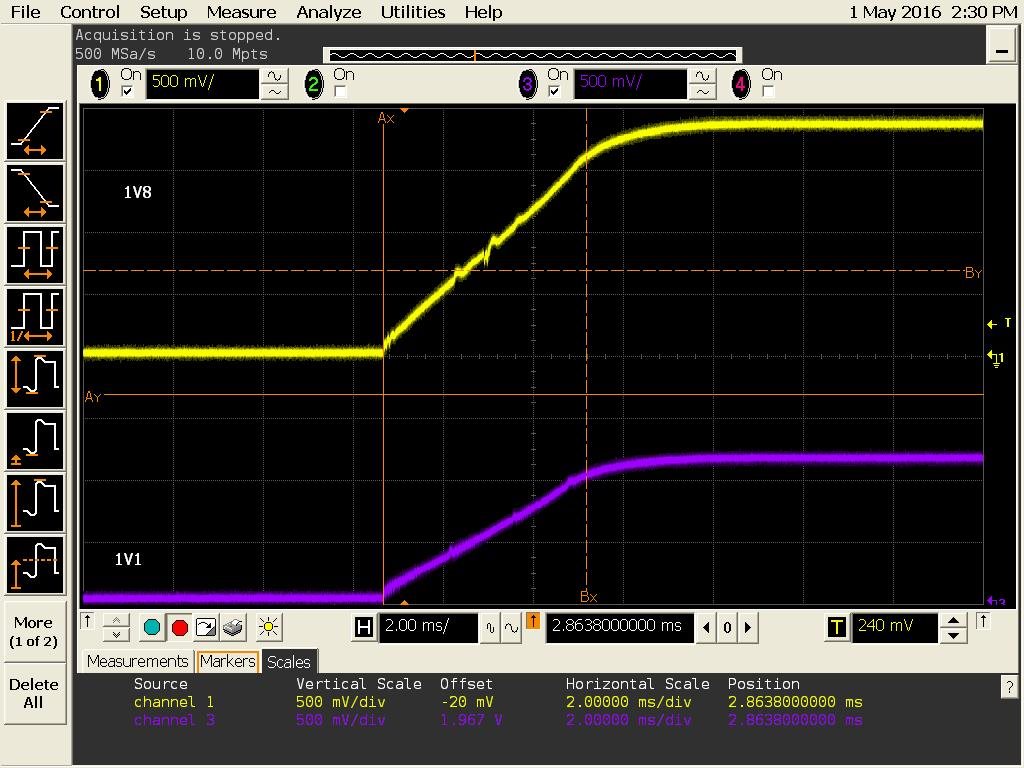

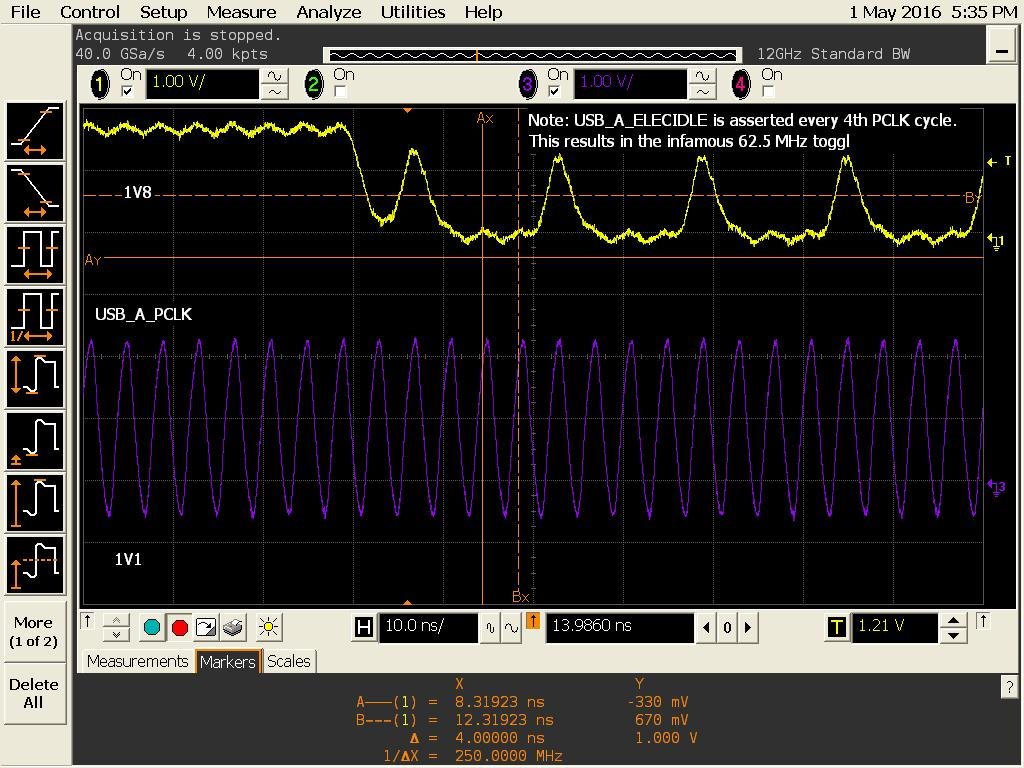

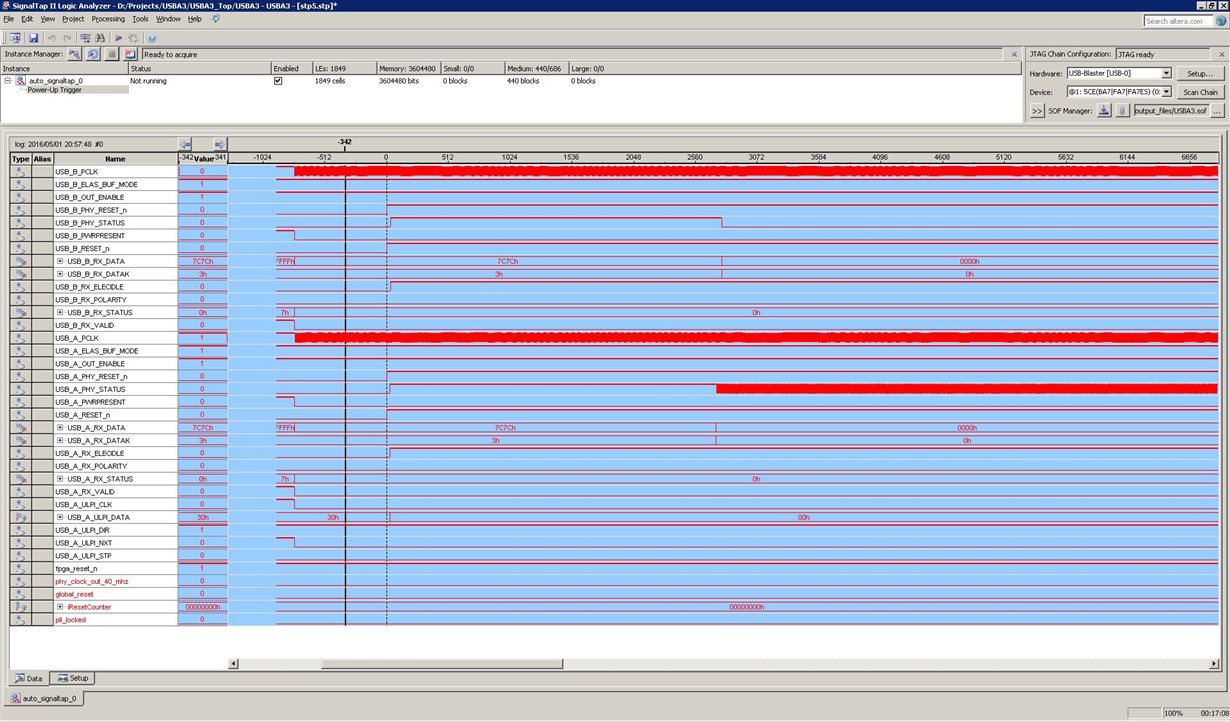

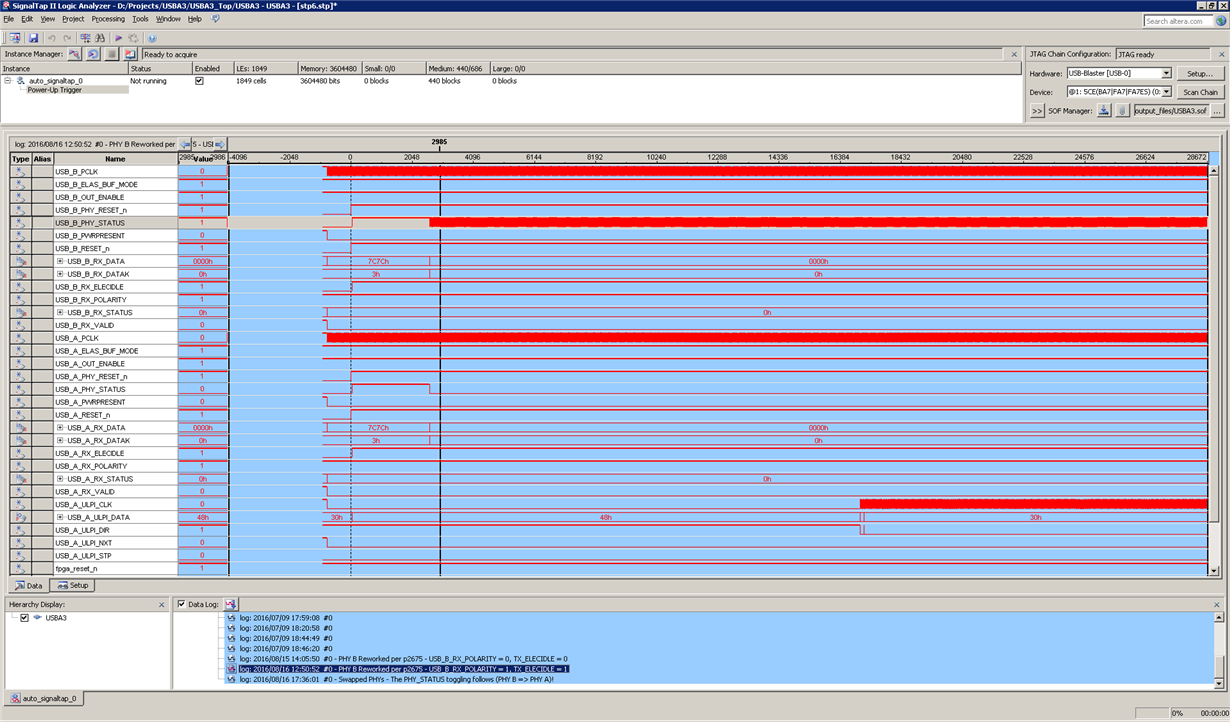

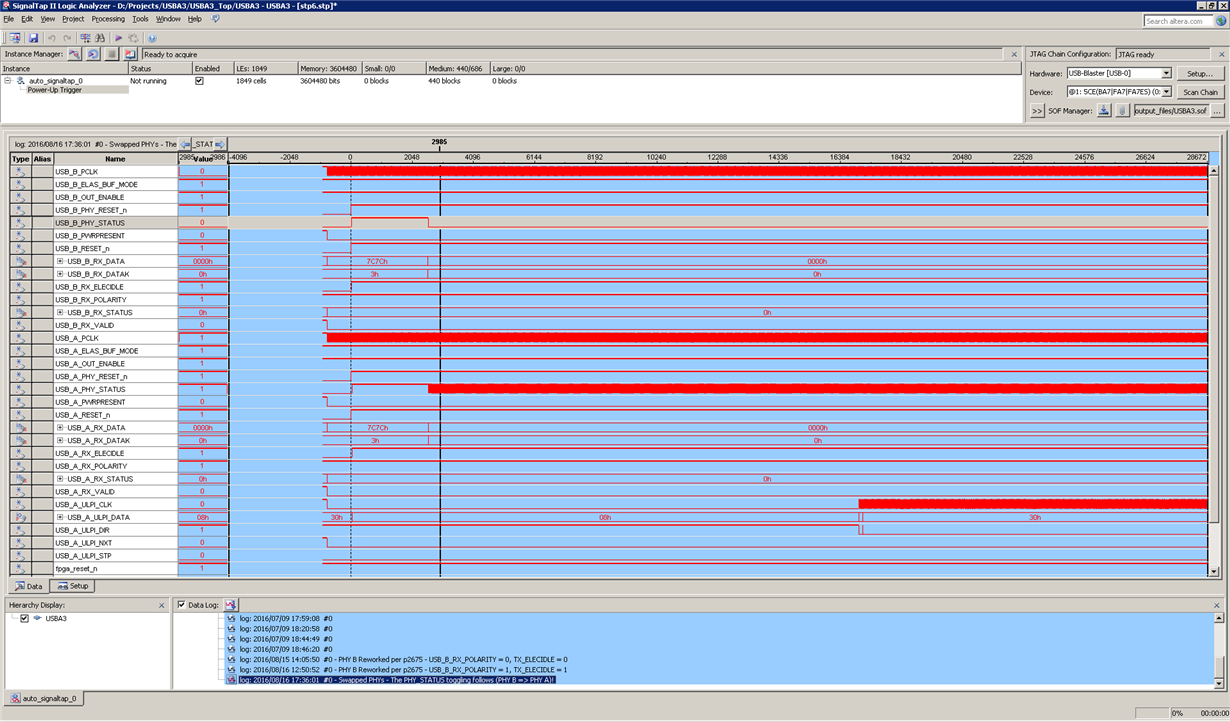

I have two identical prototype boards that have difficulties resetting the TUSB1310A parts. Each board has two TUSB1310A's but only one of the TUSB1310A's on one of the boards de-assert PHY_STATUS after coming out of reset. Only this instance of the TUSB1310A can receive data so it is certain that a bad reset is to blame.

Could you please check the attached Altera Signaltap trace to see whether anything stands out? I have spent a whole day debugging this, trying to tweak things but to no avail.

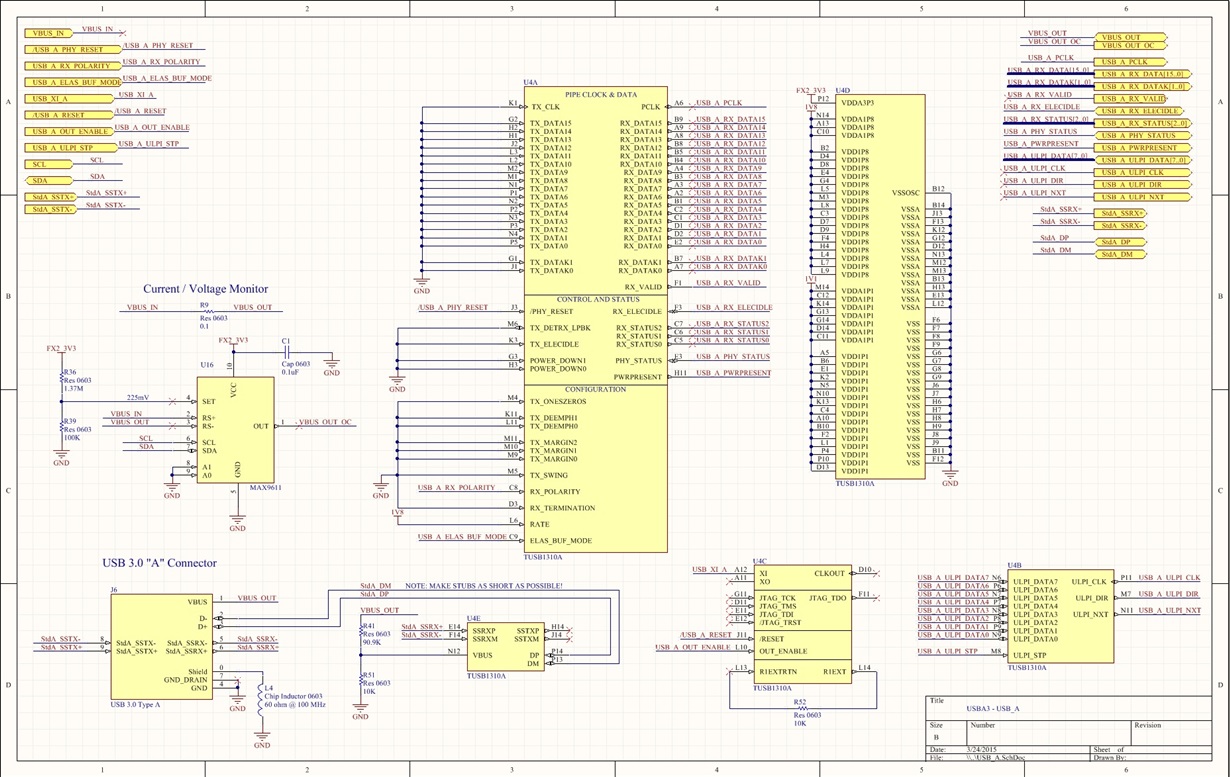

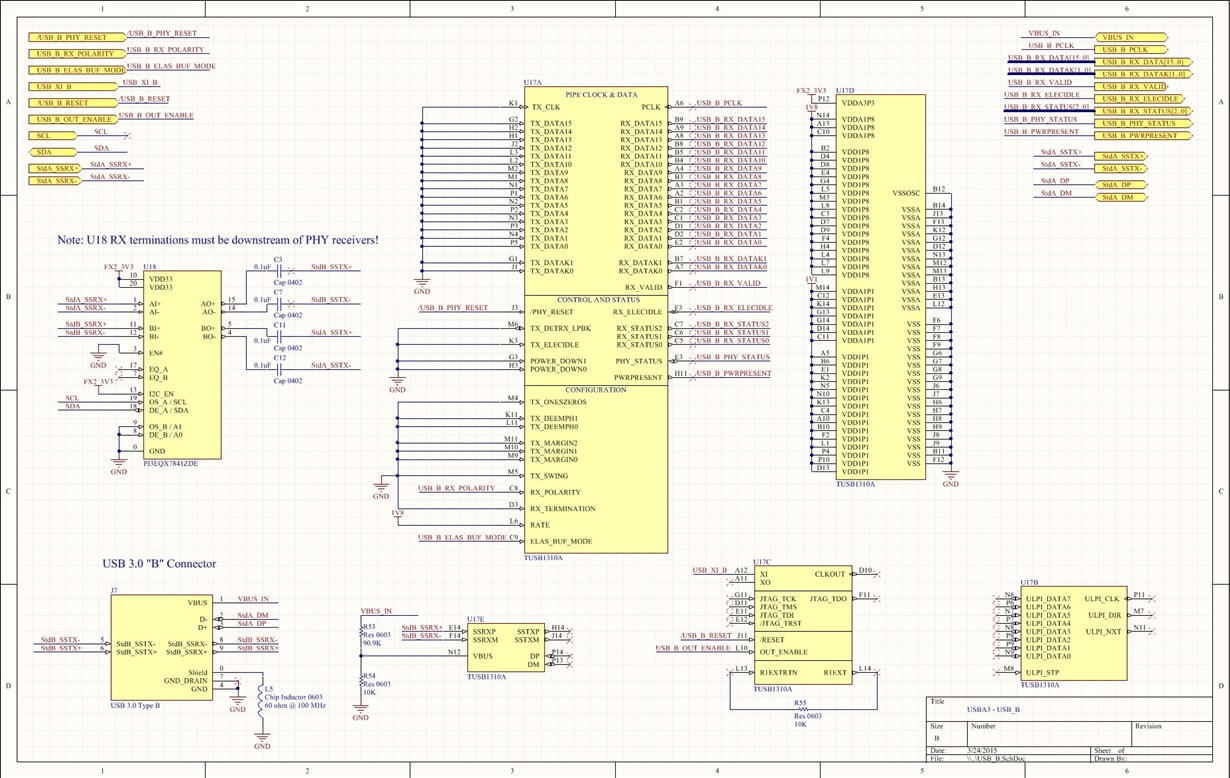

Note that only the RX path is used since this is for a USB 3.0 protocol analyzer design. Also, some pins are hard-coded per the attached schematics.

Thank you, /John.