TTL Output Frequency is 10MHz, so I can't use normal LVDS TO TTL for this application.

(LCD resolution is 480x272, and PIXEL CLK is 10MHz)

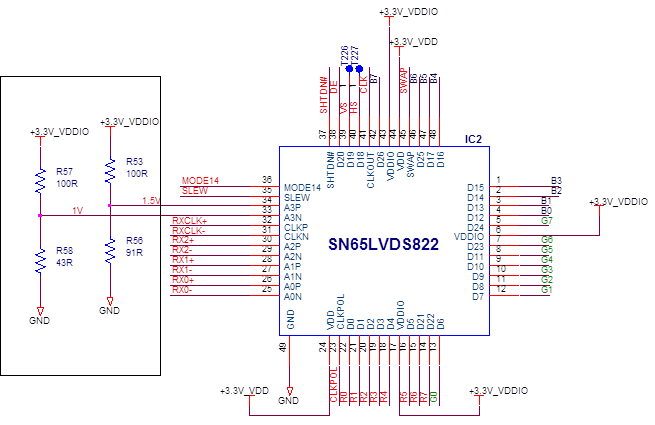

I found SN65LVDS822, but I wonder the LVDS signal is 18bit Color Host to 24bit Color LCD Panel.

My Graphic Controller use 3 channels , whether SN65LVDS822 need 4 channels for 18bit.

can I use SN65LVDS822 for this application?