Hi team,

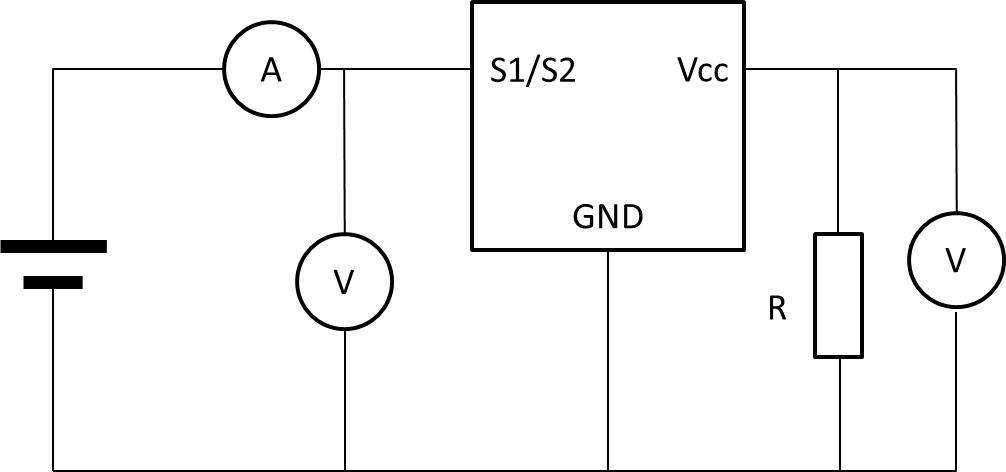

My customer would like to know I2C pin's behavior of TMDS361B(I mean S1/SCL and S2/SDA) when its power is not applied. In their circuit, one of power line connected EEPROM wakes up first to initialize a MCU, so the voltage of the line will be applyded to S1/SCL and S2/SDA pin's prior to its power supply.

Their questions is as below.

Do the S1/SCL and S2/SDA pins behave as Hi-Z under no power supply condition?

If it's "NO", we plan to recommend them switch devices to cut off current leakage.

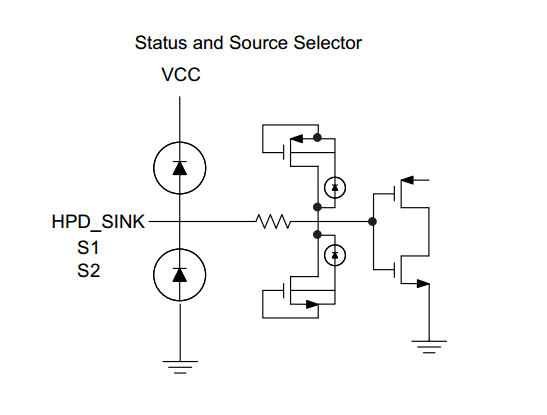

As far as I looked into the datasheet, there are a block diagram which indicates around circuit of the Pins as below. And it looks there are some diodes between the pins and Vcc. But the additional swithch it not desirable for them, so let me ask on this just in case.

Regards,

Takashi Onawa